# **SoC Blockset**<sup>™</sup> User's Guide

# MATLAB&SIMULINK®

**R**2019**a**

### **How to Contact MathWorks**

Latest news: www.mathworks.com Sales and services: www.mathworks.com/sales\_and\_services User community: www.mathworks.com/matlabcentral Technical support: www.mathworks.com/support/contact\_us Phone: 508-647-7000

The MathWorks, Inc. 1 Apple Hill Drive Natick. MA 01760-2098

SoC Blockset<sup>™</sup> User's Guide

© COPYRIGHT 2019 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### Trademarks

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### Patents

MathWorks products are protected by one or more U.S. patents. Please see www.mathworks.com/patents for more information.

#### **Revision History**

March 2019 Online Only

New for Version 1.0 (Release 2019a)

# Contents

## **Create SoC Models**

| What is Task Execution?                                    | 1-  |

|------------------------------------------------------------|-----|

| Task Execution Life Cycle                                  | 1-  |

| Task and Thread                                            | 1-  |

|                                                            |     |

| Event-Driven Tasks                                         | 1-  |

| Create a Simulink Model with an Event Driven Task          | 1-  |

| Timer-Driven Task                                          | 1-  |

| Create a Simulink Model with an Timer Driven Task          | 1-  |

| Kernel Latency                                             | 1-1 |

| Effect Kernel Latency on Task Execution                    | 1-1 |

| Task Duration                                              | 1-1 |

| Approximation Using Parameterized Probability Distribution |     |

|                                                            | 1-1 |

| Approximation Using Calculated Probability Distribution    | 1-1 |

| Specification from Task Manager Input Port                 | 1-1 |

| Replay of Recorded Task Execution Timing Data              | 1-1 |

| Value and Caching of Task Subsystem Signals                | 1-1 |

| Memory and Register Data Transfers                         | 1-1 |

| Modeling Datapath with Memory Channel Block                | 1-1 |

| Modeling Datapath with Register Channel Block              | 1-2 |

| Simplified AXI4 Master Interface                           | 1-2 |

| Simplified AXI4 Master Protocol - Write Channel            | 1-2 |

| Simplified AXI4 Master Protocol - Read Channel             | 1-2 |

| AVIA Streege Interfece                                     | 1 ' |

| AXI4-Stream Interface                                      | 1-2 |

| Simplified Streaming Protocol                              | 1-2 |

| Ready Signal (Optional)                                                                                                  | 1-28                         |

|--------------------------------------------------------------------------------------------------------------------------|------------------------------|

| AXI4-Stream Video Interface<br>Streaming Pixel Protocol<br>Protocol Signals and Timing Diagrams                          | 1-30<br>1-30<br>1-31         |

| Models with I/O Device Blocks<br>Processor I/O with Memory Model<br>Processor I/O with Network Device Model              | 1-34<br>1-34<br>1-34         |

| Use Template to Create SoC Model<br>Create SoC Model Using SoC Blockset Template<br>Template Structure<br>Modify Project | 1-35<br>1-35<br>1-37<br>1-37 |

| HDMI Template         Required Products         Template Structure         Modify Project                                | 1-40<br>1-40<br>1-40<br>1-41 |

| Frame Buffer with HDMI Template                                                                                          | 1-43<br>1-43<br>1-43<br>1-44 |

| Stream from FPGA to Processor Template         Required Products         Template Structure         Modify Project       | 1-47<br>1-47<br>1-47<br>1-48 |

| SDR Template                                                                                                             | 1-51<br>1-51<br>1-51<br>1-52 |

| Considerations for Multiple IPs in FPGA Model                                                                            | 1-56                         |

| Create an SoC Project Application                                                                                        | 1-57                         |

| Project and Top-Level Model                                                                                              | 1-58                         |

| Software and Task Management on Processor<br>Processor Model                                                             | 1-61<br>1-61                 |

| Task Processing                                             | 1-62 |

|-------------------------------------------------------------|------|

| Top Model                                                   | 1-64 |

| User Logic on FPGA                                          | 1-65 |

| Sample Based Model                                          | 1-65 |

| Top Model                                                   | 1-67 |

| Memory and Register Channel Connections                     | 1-69 |

| Memory Channel Connection                                   | 1-69 |

| Register Channel Connection                                 | 1-70 |

| Simulation and Analysis                                     | 1-72 |

| Entities in an SoC Blockset Model                           | 1-73 |

| Visualize Entities                                          | 1-73 |

| Generators and Terminators                                  | 1-73 |

| Custom Hardware Board Configuration                         | 1-75 |

| Build Error for Accelerator Mode and Rapid Accelerator Mode |      |

|                                                             | 1-76 |

# **Simulate SoC Applications**

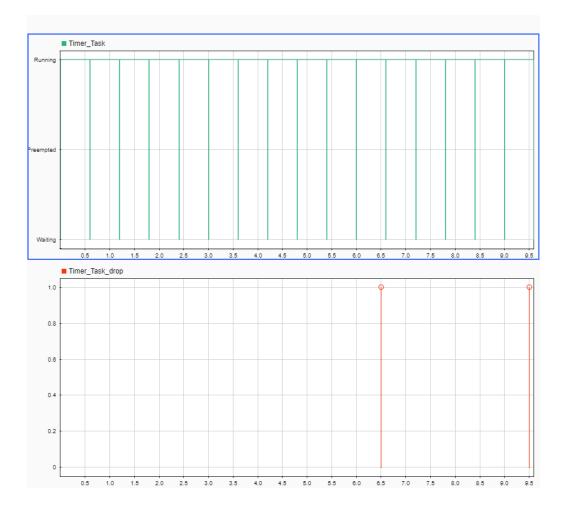

| Task Overruns and CountermeasuresReduction of Task Execution IntervalDistribution of Tasks Across Multiple Processor CoresDropping Overrunning Tasks | 2-2<br>2-3<br>2-3<br>2-3     |

|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Task Execution Playback using Recorded Data                                                                                                          | 2-9                          |

| Task Priority and Preemption            Preemption of Low Priority Task by High Priority Task                                                        | 2-10<br>2-10                 |

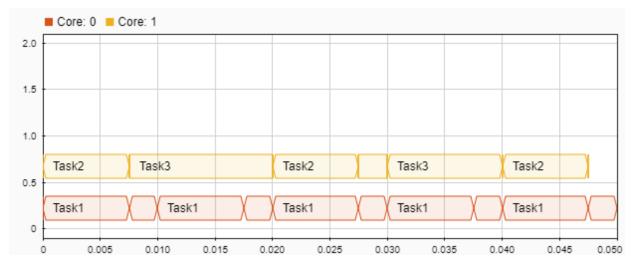

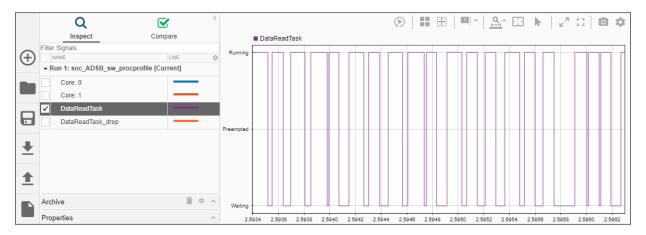

| Multicore Execution and Core VisualizationSpecify the Core for a TaskCore Visualization in Simulation Data InspectorMulti-Core Task Execution        | 2-14<br>2-14<br>2-14<br>2-16 |

| Recording Tasks for Use in Simulation                  | 2-18 |

|--------------------------------------------------------|------|

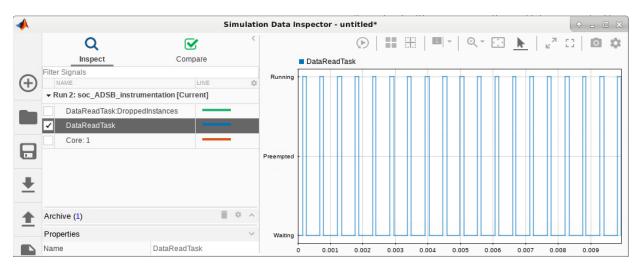

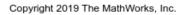

| Task Visualization in Simulation Data Inspector        | 2-20 |

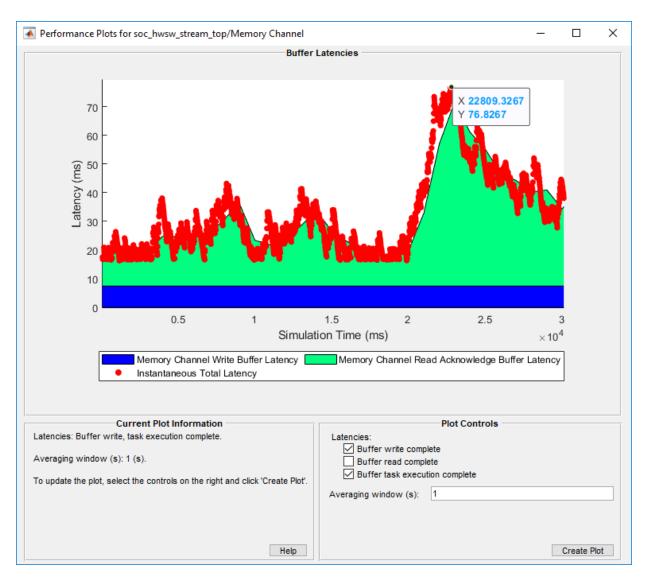

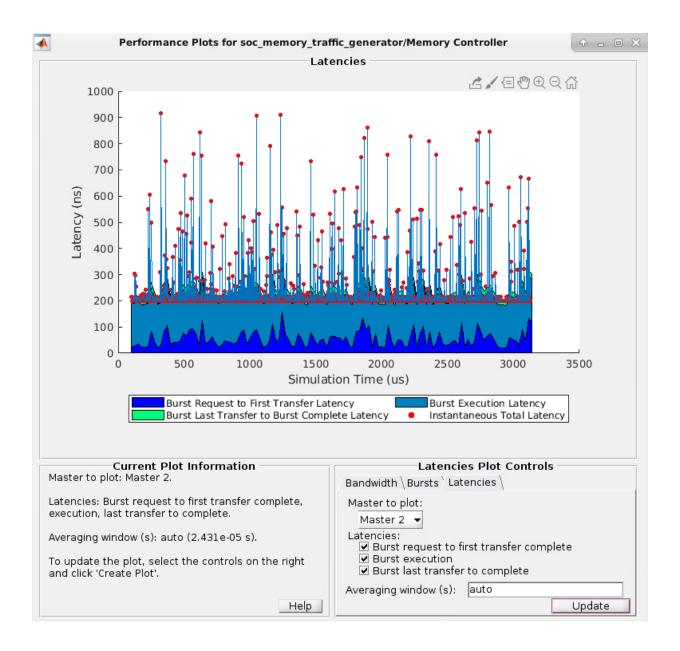

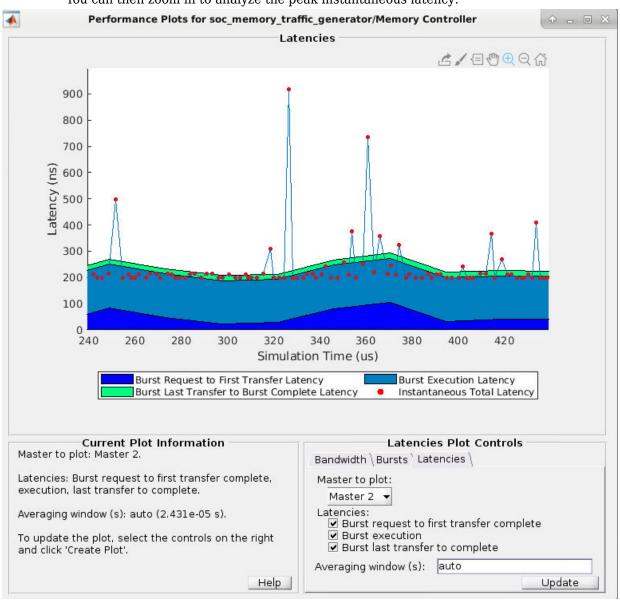

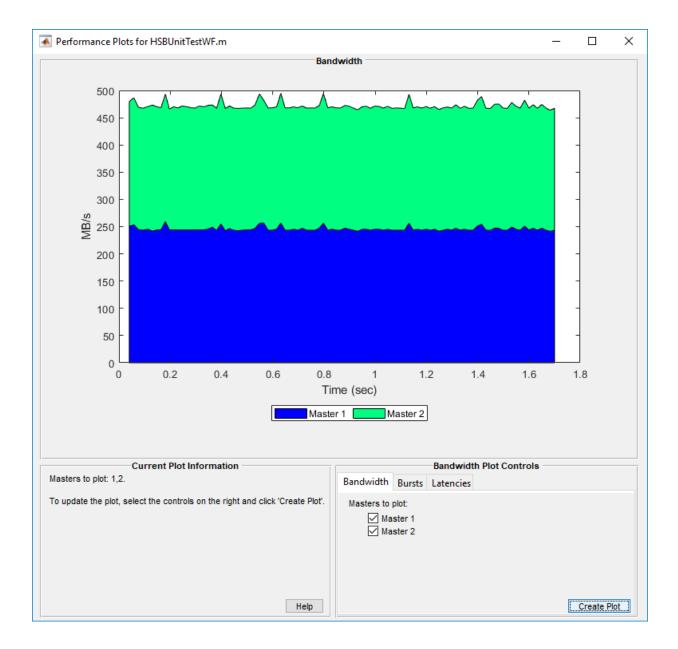

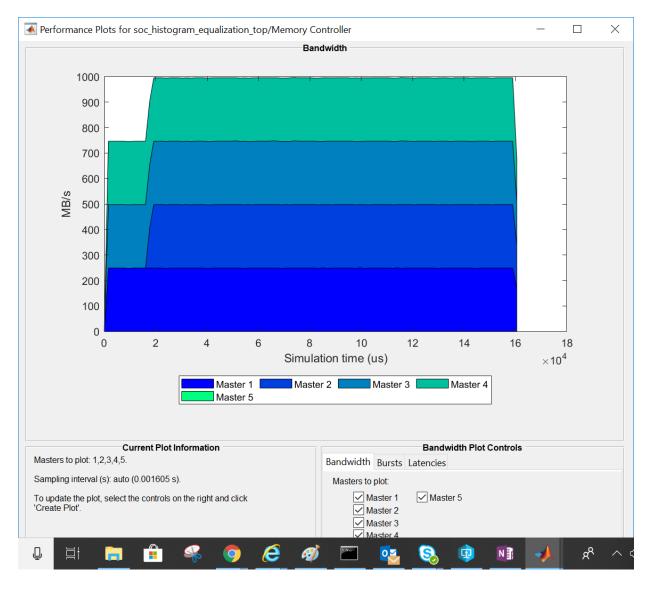

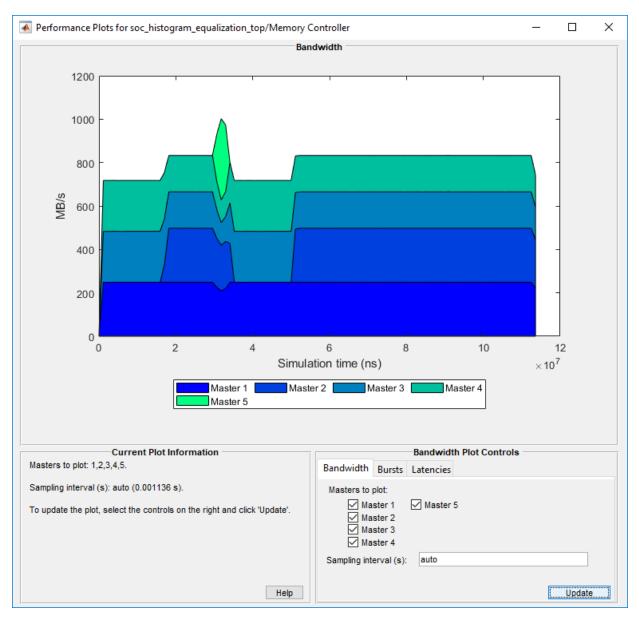

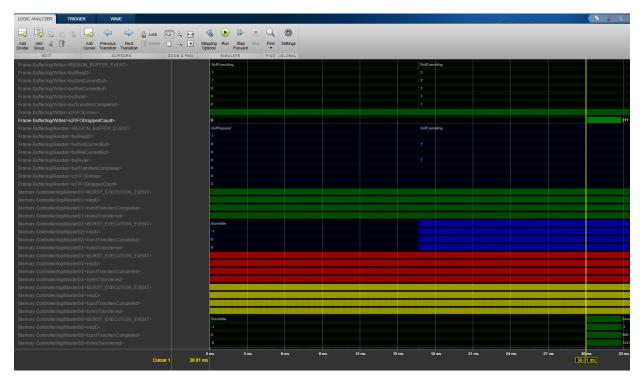

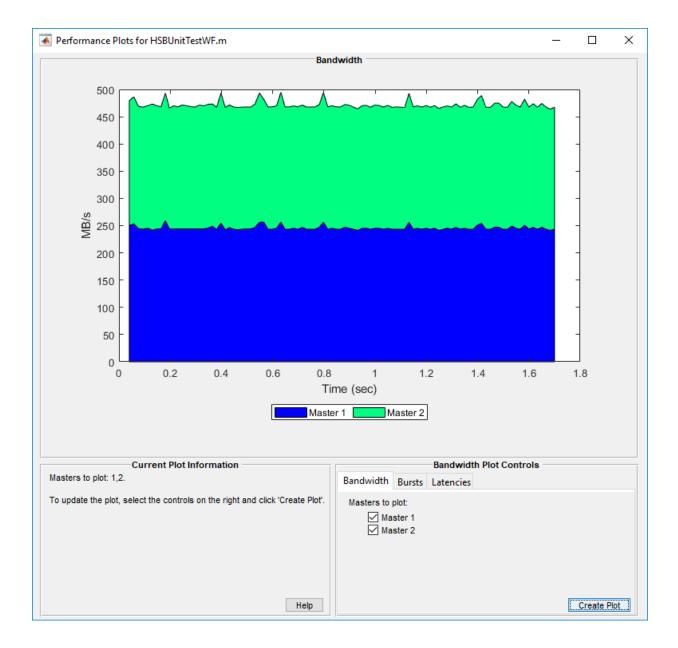

| Simulation Performance Plots                           | 2-22 |

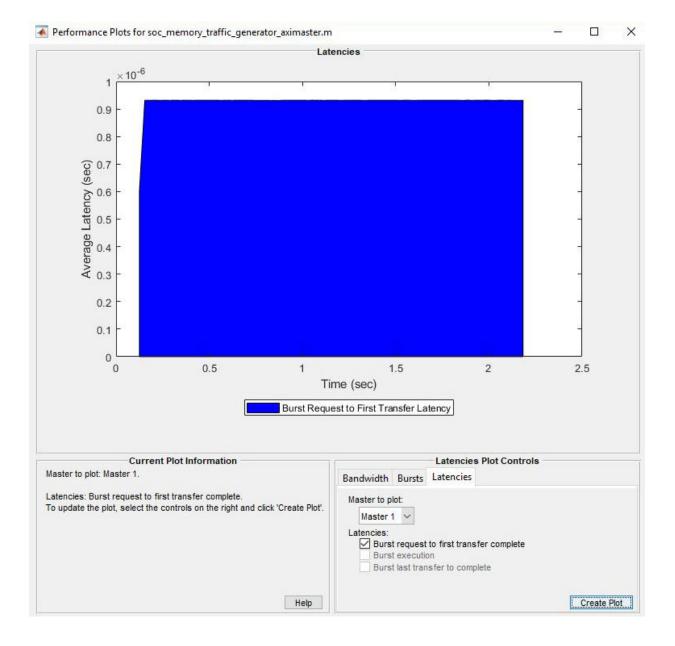

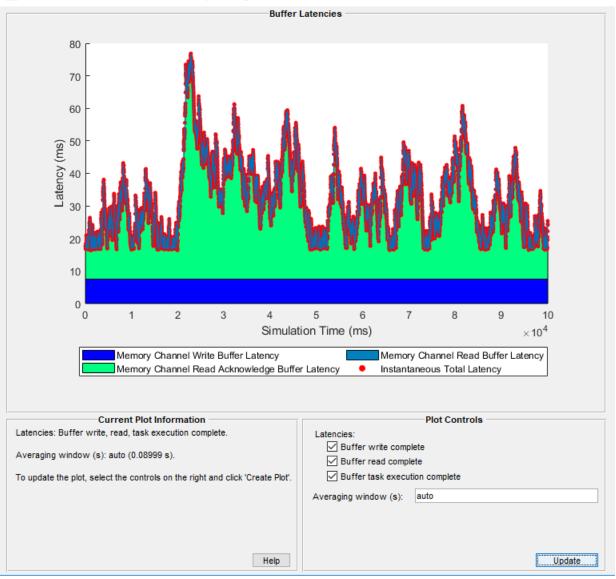

| Memory Channel Latency Plots                           | 2-23 |

| Memory Controller Latency Plots                        | 2-27 |

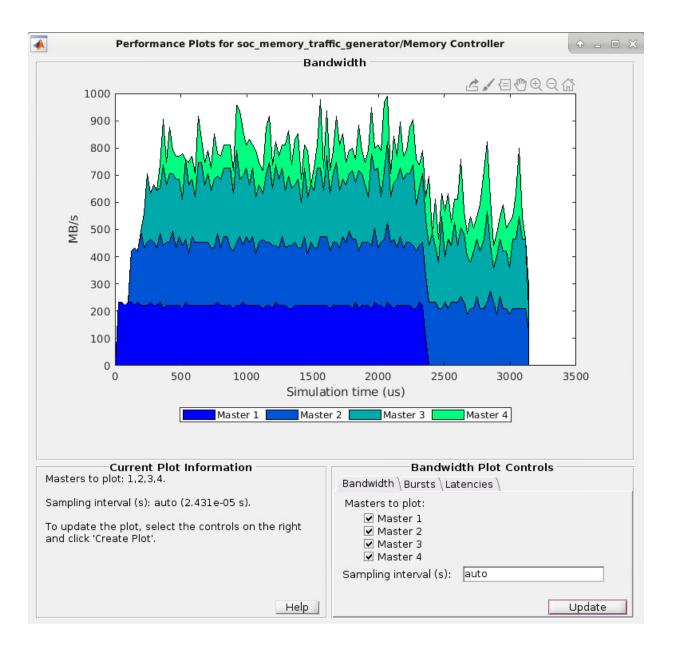

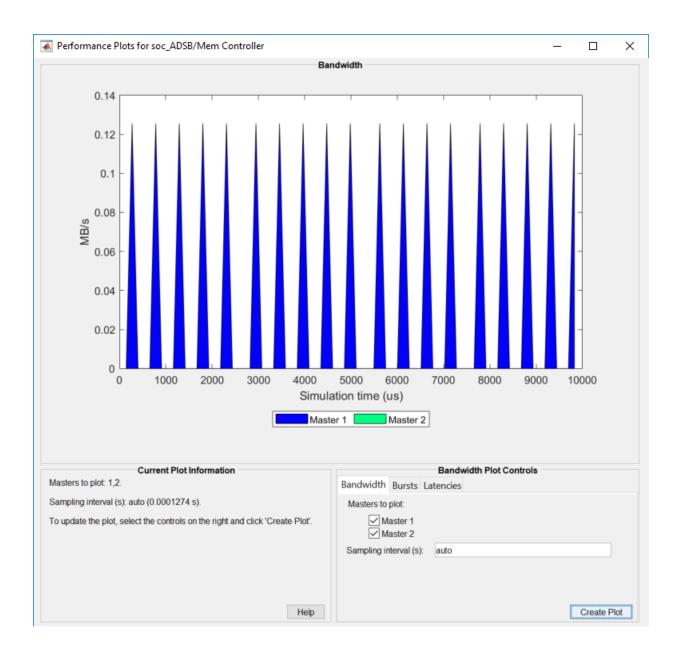

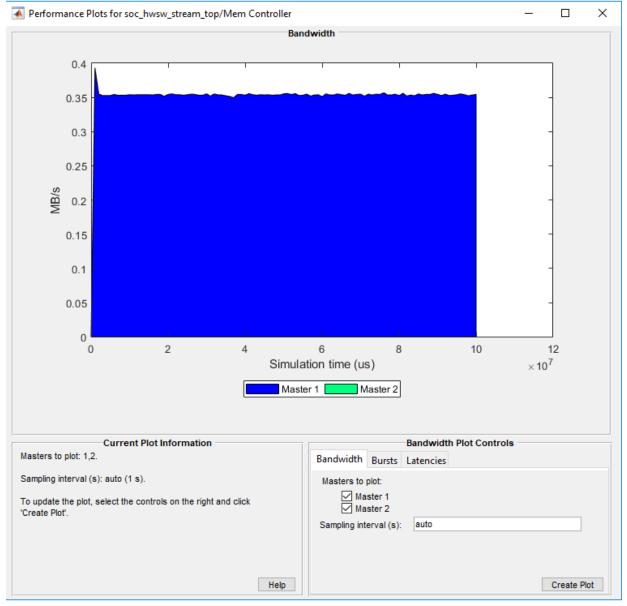

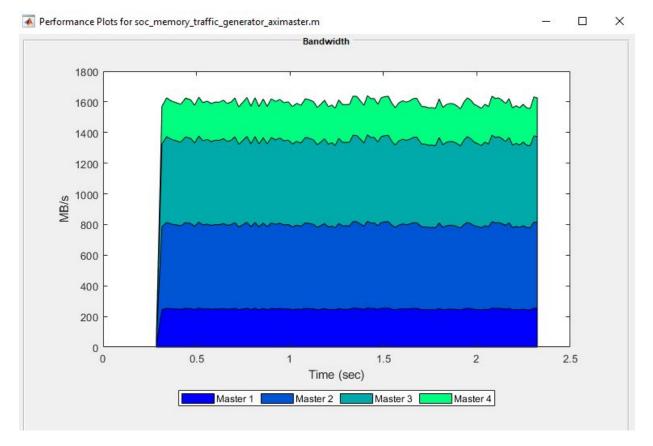

| Memory Bandwidth Plots                                 | 2-31 |

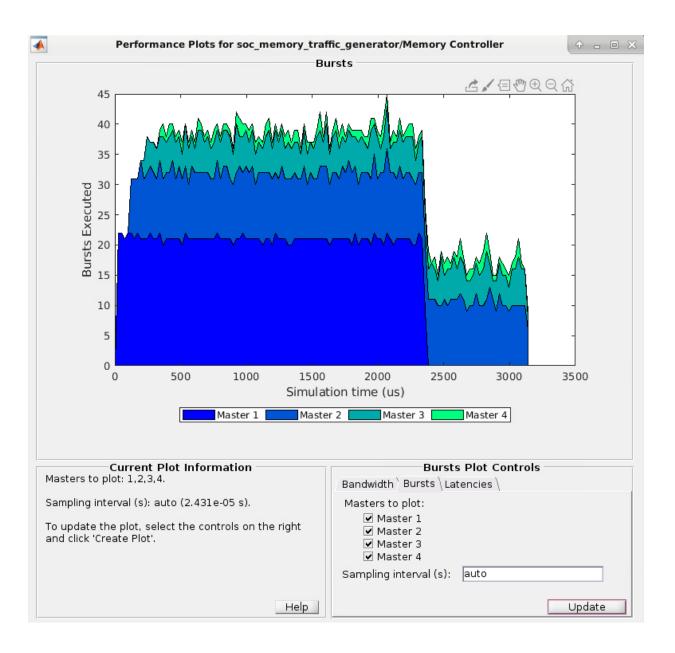

| Memory Burst Plots                                     | 2-33 |

| Simulation Diagnostics                                 | 2-36 |

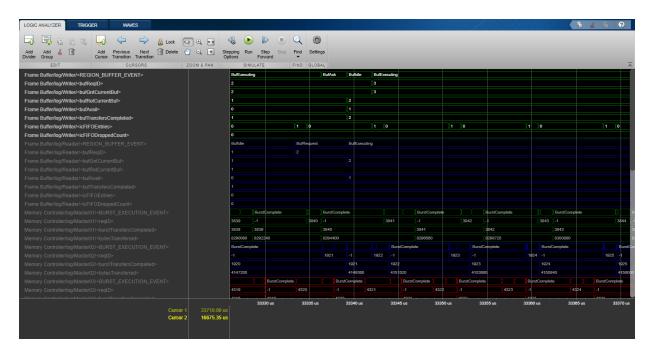

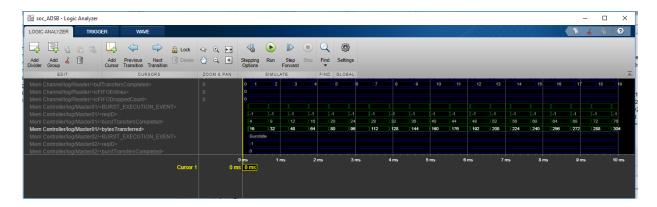

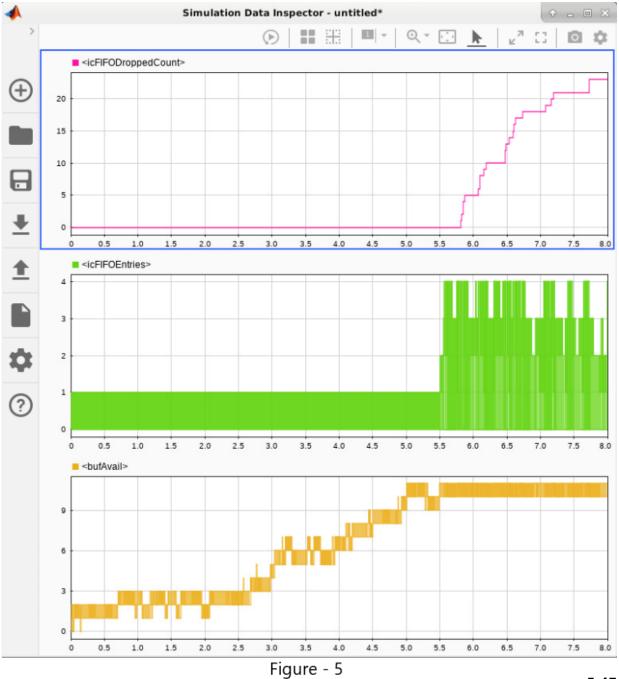

| Buffer and Burst Waveforms                             | 2-36 |

| External Memory Channel Protocols                      | 2-41 |

| AXI4 Stream to Software via DMA                        | 2-41 |

| AXI4 Stream FIFO                                       | 2-41 |

| AXI4 Stream Video FIFO                                 | 2-41 |

| AXI4 Stream Video Frame Buffer                         | 2-42 |

| AXI4 Random Access                                     | 2-42 |

| Channel Data and Memory Bursts                         | 2-42 |

| Guidelines for Setting Burst and Buffer Parameters     | 2-43 |

| Memory Channel Model Fidelity                          | 2-46 |

| Record Data from Hardware I/O Devices                  | 2-47 |

| Process to Record Data                                 | 2-47 |

| Use Memory and I/O Device Data in Processor Simulation | 2-48 |

| Event-Driven Task                                      | 2-48 |

| Timer-Driven Task                                      | 2-48 |

# Generate Code and Deploy on SoC Device

| Supported Third-Party Tools and Hardware        | 3-2         |

|-------------------------------------------------|-------------|

| Third-Party Synthesis Tools and Version Support | 3-2         |

| Third-Party Support for Software Generation     | 3-2         |

| Supported Xilinx Devices                        | 3-2         |

| Supported Intel Devices                         | 3-2         |

| SoC Board Support Packages                      | <b>3-</b> 3 |

| Configure Design for Generation                     | 3-4  |

|-----------------------------------------------------|------|

| Create FPGA Model and Include It in Top-Level Model | 3-4  |

| Configure Reference Design                          | 3-4  |

| FPGA Model Guidelines                               | 3-5  |

| Code Generation of Software Tasks                   | 3-7  |

| Timer-Driven Tasks                                  | 3-7  |

| Event-Driven Task                                   | 3-7  |

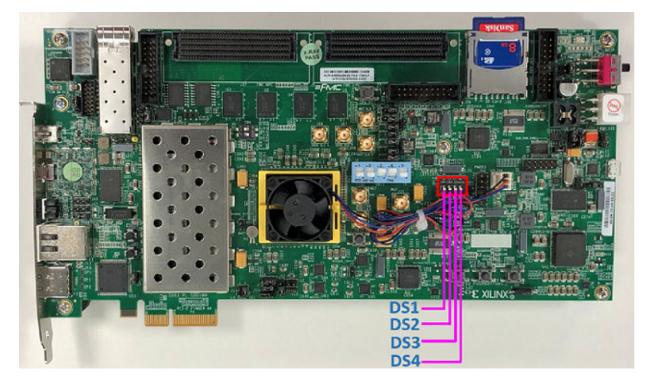

| Configure and Run Design on Hardware                | 3-8  |

| Load FPGA Bitstream                                 | 3-8  |

| Configure and Run AXI Master JTAG Test bench Script | 3-8  |

| Generate SoC Design                                 | 3-12 |

| Step 1: Set Up FPGA Design Software Tools           | 3-12 |

| Step 2: Start SoC Builder                           | 3-13 |

| Step 3: Prepare Model for Generation                | 3-13 |

| Step 4: Select Project Folder                       | 3-15 |

| Step 5: Select Build Action                         | 3-15 |

| Step 6: Validate Model                              | 3-16 |

| Step 7: Build Model                                 | 3-16 |

| Step 8: Connect Hardware                            | 3-16 |

| Step 9: Load and Run                                | 3-17 |

# **Analyze Performance on SoC Device**

| Code Instrumentation Profiler                         | 4-2  |

|-------------------------------------------------------|------|

| Limitations                                           | 4-3  |

| Profile Task Execution on Processor                   | 4-4  |

| Task Profiling with External Mode                     | 4-4  |

| Memory Performance Information from FPGA Execution    | 4-6  |

| Performance Plots                                     | 4-8  |

| Burst Waveforms                                       | 4-12 |

| Configuring and Querying the AXI Interconnect Monitor | 4-13 |

# Examples

| Random Access of External Memory                  | 5-2   |

|---------------------------------------------------|-------|

| Packet-Based ADS-B Transceiver                    | 5-11  |

| Histogram Equalization Using Video Frame Buffer   | 5-24  |

| Streaming Data from Hardware to Software          | 5-37  |

| Analyze Memory Bandwidth Using Traffic Generators | 5-51  |

| Record I/O Data from SoC Device                   | 5-64  |

| Simulate with I/O Data Recorded from SoC Device   | 5-71  |

| Task Execution                                    | 5-74  |

| Timer-Driven Task                                 | 5-97  |

| Event-Driven Task                                 | 5-100 |

# **Supported Hardware**

| 6 | [ |

|---|---|

| - | I |

| SoC Blockset Supported Hardware |  | 6-2 |

|---------------------------------|--|-----|

|---------------------------------|--|-----|

# **Create SoC Models**

- "What is Task Execution?" on page 1-2

- "Event-Driven Tasks" on page 1-4

- "Timer-Driven Task" on page 1-8

- "Kernel Latency" on page 1-11

- "Task Duration" on page 1-14

- "Value and Caching of Task Subsystem Signals" on page 1-18

- "Memory and Register Data Transfers" on page 1-19

- "Simplified AXI4 Master Interface" on page 1-23

- "AXI4-Stream Interface" on page 1-27

- "AXI4-Stream Video Interface" on page 1-30

- "Models with I/O Device Blocks" on page 1-34

- "Use Template to Create SoC Model" on page 1-35

- "HDMI Template" on page 1-40

- "Frame Buffer with HDMI Template" on page 1-43

- "Stream from FPGA to Processor Template" on page 1-47

- "SDR Template" on page 1-51

- "Considerations for Multiple IPs in FPGA Model" on page 1-56

- "Create an SoC Project Application" on page 1-57

- "Project and Top-Level Model" on page 1-58

- "Software and Task Management on Processor" on page 1-61

- "User Logic on FPGA" on page 1-65

- "Memory and Register Channel Connections" on page 1-69

- "Simulation and Analysis" on page 1-72

- "Entities in an SoC Blockset Model" on page 1-73

- "Custom Hardware Board Configuration" on page 1-75

- "Build Error for Accelerator Mode and Rapid Accelerator Mode" on page 1-76

# What is Task Execution?

A task is a unit of execution or unit of work in a software application. Typically, task execution in an embedded processor is managed by the operating system (OS). When deployed to the embedded processor, a task corresponds to an OS thread. The SoC Blockset defines the execution life cycle and relation to OS threads as follows.

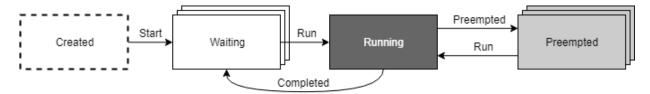

### **Task Execution Life Cycle**

The life cycle of a task can be divided into five states:

- *Created* The system creates all the tasks when the application starts and immediately moves them to the waiting state.

- *Waiting* The task waits for the associated trigger signal, such as an OS timer or I/O device. After receiving the trigger signal, the task starts to run. If the task has the highest priority, it enters the running state. Otherwise, the task continues to wait until it becomes the highest priority, triggered task.

- *Running* The task executes its code. When the code completes execution, the task immediately moves to the waiting state. If a trigger for a higher-priority task occurs, the running task moves to the preempted state.

- *Preempted* The task is preempted and waiting to run. A task runs based on a combination of the task priority and the order the task entered the *Preempted* state. Assuming equal task priorities of all other tasks in *Ready to Resume* state, tasks run based on first-in-first-out (FIFO) ordering.

- *Terminated* Tasks terminate when the application ends.

This figure shows the state diagram of a task execution life cycle for an application using an OS. For simplicity, the terminated state is not shown, but a task can reach the terminated state from any of the other states.

### **Task and Thread**

A task is a conceptual unit of work in an algorithm. In an application executing on a device, a task is a section of code that executes in a thread within an operating system (OS). The OS thread determines the state of execution of the task. Within the SoC Blockset, a task specifically refers to the portion of the Simulink<sup>®</sup> model contained within a rate or function-call subsystem. The trigger signal for that subsystem comes from a Task Manager block. When deployed to hardware, an OS thread uses the task properties. The thread executes the code generated from the subsystem. Conceptually, a *Task* in simulation is equivalent to a *thread* in generated code.

# See Also

Task Manager

## **More About**

- "Timer-Driven Task" on page 1-8

- "Event-Driven Tasks" on page 1-4

## **External Websites**

• Task (computing)

# **Event-Driven Tasks**

Event-driven tasks start executing when triggered by an external event. Events can include internal events, such as memory stream or register writes, or external events, such as receiving a UDP data packet from a network connection. Assuming no other tasks are executing at the time of the event or the task has the highest priority, the event-driven task can respond immediately to the event. The task can then process the received data, and potentially generate other events in the model.

#### **Create a Simulink Model with an Event Driven Task**

This example shows how to create and configure a Simulink  ${\ensuremath{\mathbb R}}$  model to use the event driven task feature of the SoC Blockset.

#### **Create a Software Reference Model**

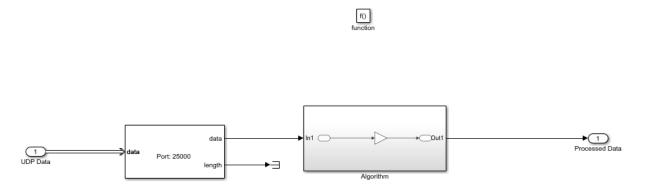

This section shows how to create a reference model of the software for an SoC application model. The software contains an event driven task subsystem that reacts to receiving UDP packets.

- **1** Create a new blank model.

- **2** In the Simulink editor, add a Function-Call Subsystem block to the model. Connect an Inport block to the input port of the Function-Call Subsystem block. Connect the output port to a Termclcinator block.

- **3** Add an Asynchronous Task Specification block to the model. On the Block Parameters dialog box, set the **Task priority** to **41**.

- **4** Connect the output port of Asynchrnous Task Specification block to the function() input of the Function-Call Subsystem block.

- 5 Add an Inport block and open the Block parameters dialog box. On the Signal Attributes tab, check Output function call. Connect the Inport block to the input port of the Asynchronous Task Specification block.

- **6** Open the Function-Call subsystem model.

- 7 Add a UDP Read block to model. Open the Block Parameters dialog box, set Maximum data length (elements) to 1024 and check Enable event-based execution.

- 8 Connect the Inport block to the UDP Read block **UDP Data** port. Connect the **Data** port to the Outport block. Connect the **Length** port to a Terminator block.

- 9 Open the Configuration Parameters dialog box, select the Solver pane. Set Solver selection > Type to Fixed-step and check Tasking and sample timer options > Higher priority value indicates higher task priority.

- 10 Select the Hardware Implementation pane, set Hardware board to Zedboard.

- **11** Save the model as soc\_task\_createeventdriventask\_software.slx.

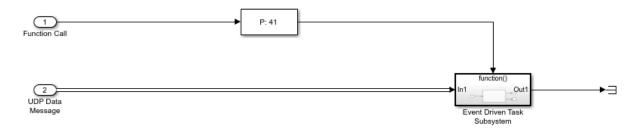

The completed model should look similar to the following model.

#### **Create the SoC Application Model**

This section shows how to create the top level SoC application model that contains the software reference model developed in the previous section.

- **1** Create a new blank model.

- 2 In the Simulink editor, add a Model block. On the Block Parameters dialog box, set **Model name** to soc\_task\_createeventdriventask\_software.slx.

- 3 Add a Task Manager block and open the Block Parameters dialog box. Set the Main > Type to Event-driven and Main > Priority to 41. Each newly added event-driven task exposes an event message input port on the Task Manager block.

- **4** (Optional) On the **Simulation** tab, you specify the task duration for that task. For more information on setting task duration, see Task Duration.

- **5** In the editor, add an IO Data Source block to the model. Open the Block Parameters dialog box and enable **Show event port**.

- 6 Connect the IO Data Source block **Event** port to the Task Manager and the **UDP Data** port to the UDP Data Message port on the Model reference block.

- 7 Open the Configuration Parameters dialog box, select the Solver pane. Set Solver selection > Type to Fixed-step and check Tasking and sample timer options > Higher priority value indicates higher task priority.

- 8 Select the Hardware Implementation pane, set Hardware board to Zedboard.

- 9 Update the diagram, press Ctrl+D.

- **10** Save the model as soc\_task\_createeventdriventask\_application.slx.

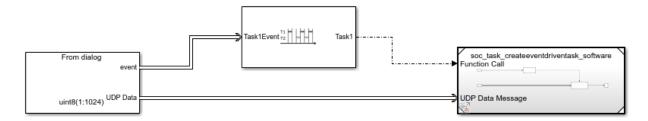

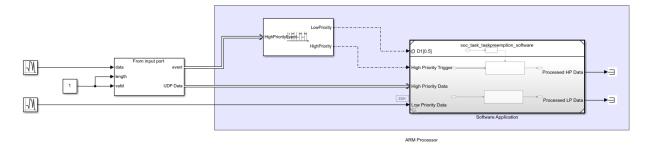

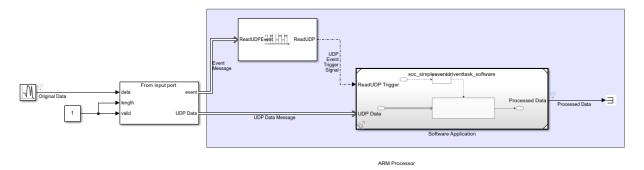

The completed model should look similar to the following model.

#### Run the Model with Event Driven Task

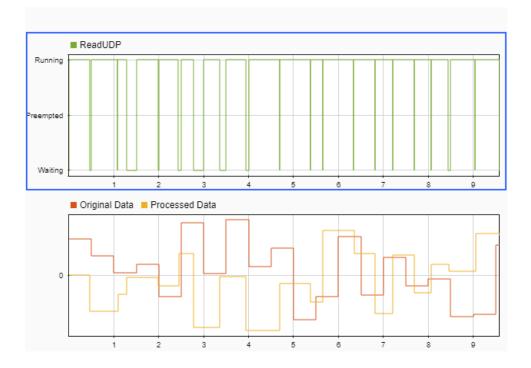

In the Simulink editor, run the

$soc_task_createeventdriventask_application.slx model.$  When the run completes, open the Simulation Data Inspector (SDI) and select **Task1**. The SDI display shows that **Task1** triggers and executes each time a new UDP packet arrives. Although superficially the task execution appears periodic, this is only a byproduct of the current default settings of the IO Data Source block that generates the event with a time step of 0.1.

# See Also

I/O Data Source | Task Manager

## **More About**

- "What is Task Execution?" on page 1-2

- "Timer-Driven Task" on page 1-8

# **Timer-Driven Task**

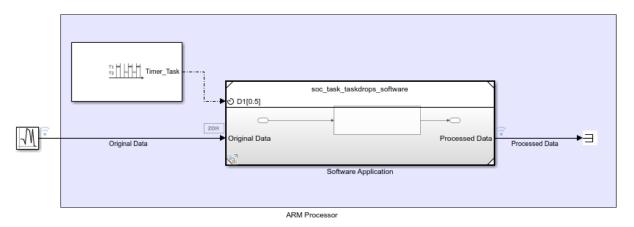

Timer-driven tasks execute at a periodic rate equal to an integer multiple of the Simulink model fundamental sample time.

To create a timer-driven task, connect the task port of a Task Manager block to a periodic event port on a Model block. Each rate in a Model block generates a unique model periodic event port with the time step for the rate shown on the block icon. In the Model block dialog mask, use the **Schedule rates** parameter to enable model periodic event ports.

**Note** A timer-driven task requires a lower priority than an event-driven task.

#### **Create a Simulink Model with an Timer Driven Task**

This example shows how to create and configure a Simulink(r) model to use the timer driven task feature of the SoC Blockset.

#### **Create a Software Reference Model**

This section shows how to create a reference model of the software for an SoC application model. The software contains one timer driven task subsystem that reacts to receiving UDP packets.

- **1** Create a new blank model.

- 2 In the Simulink editor, add a Subsystem block to the model. Add a Sine block and connect it to the Subsystem block. Connect the output of the Subsystem block to a Terminator block.

- **3** Open the Function-Call subsystem model.

- 4 Open the Block parameteres dialog box of the Inport block, set the **Sample Time** to 0.1.

- 5 In the Simulink editor, open the Configuration Parameters dialog box.

- 6 Select the Hardware Implementation pane, set Hardware board to Zedboard.

- 7 Save the model as soc\_task\_createtimerdriventask\_software.slx.

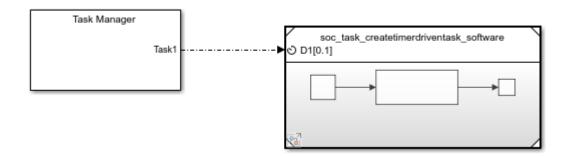

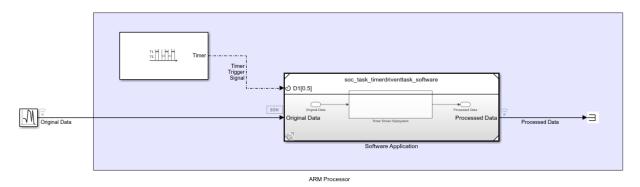

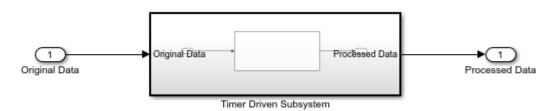

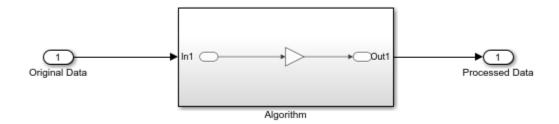

The completed model should look similar to the following model.

#### **Create the SoC Application Model**

This section shows how to create the top level SoC application model that contains the software reference model developed in the previous section.

- **1** Create a new blank model.

- 2 In the Simulink editor, add a Model block and open the Block Parameters dialog box.

- 3 Check Main > Schedule Rates and set Main > Model name to soc\_task\_createtimerdriventask\_software.slx.

- 4 In the editor, add a Task Manager block to the model.

- 5 (Optional) Open the Block Parameters dialog box of the Task Manager block. By default, the task Type is Timer-driven with a Period of 0.1. On the Simulation tab, you specify the task duration for that task. For more information on setting task duration, see Task Duration.

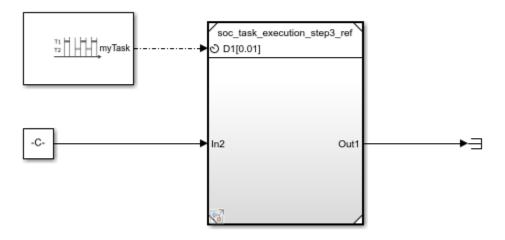

- 6 In the editor, connect the **Task1** port to the **D1[0.1]** port of the Model block.

- 7 Open the Configuration Parameters dialog box, select the **Hardware Implementation** pane, set **Hardware board** to Zedboard.

- 8 Update the diagram, press Ctrl+D.

- 9 Save the model as soc\_task\_createtimerdriventask\_application.slx.

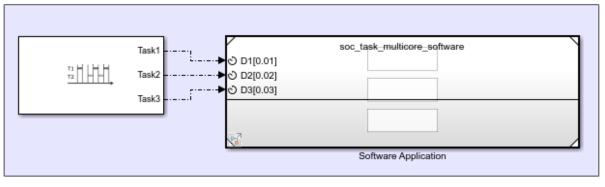

The completed model should look similar to the following model.

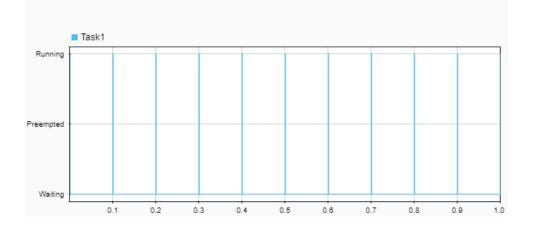

#### Run the Model with Timer Driven Task

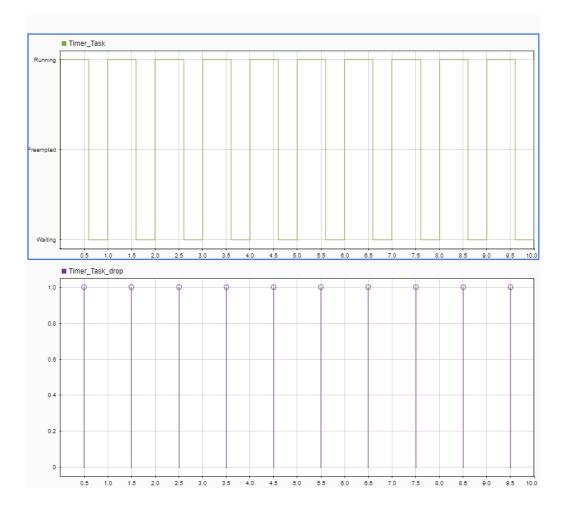

In the Simulink editor, run the

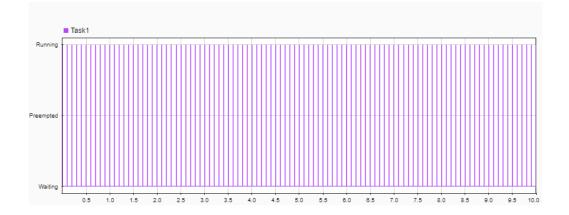

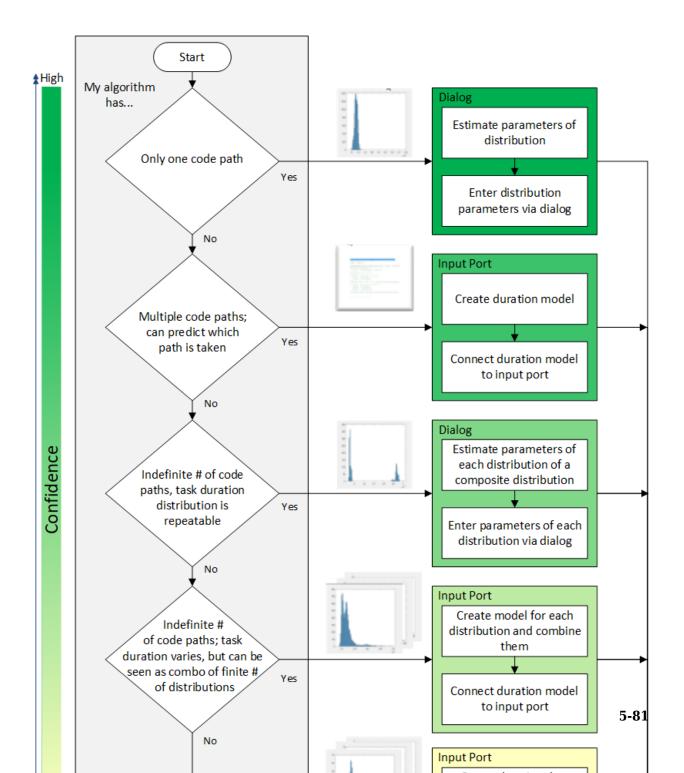

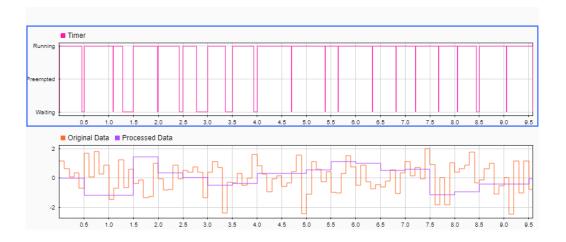

soc\_task\_createtimerdriventask\_application.slx model. When the run completes, open the Simulation Data Inspector (SDI) and select Task1. The SDI display shows that Task1 triggers each 0.1 time steps.

# See Also

Task Manager

## **More About**

- "What is Task Execution?" on page 1-2

- "Event-Driven Tasks" on page 1-4

# **Kernel Latency**

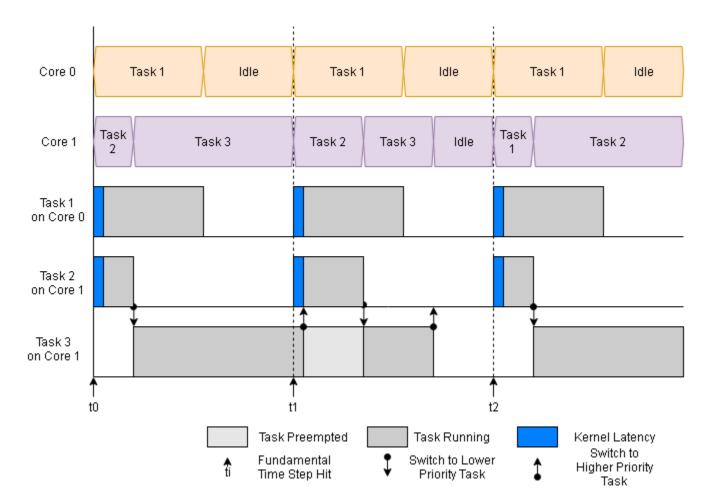

In a deployed application, switching between threads requires a finite amount of time depending on the current state of the thread, embedded processor, and OS. *Kernel latency* defines the time required for the operating system to respond to a trigger signal, stop execution of any running threads, and start the execution of the thread responsible for the trigger signal.

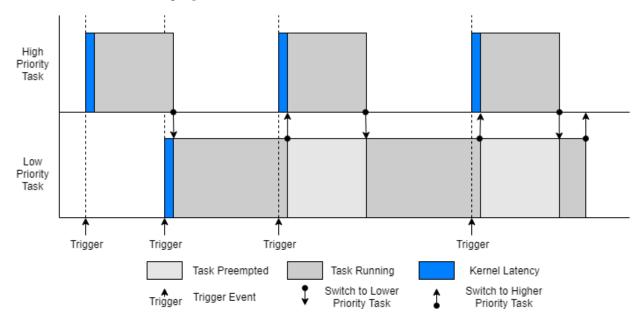

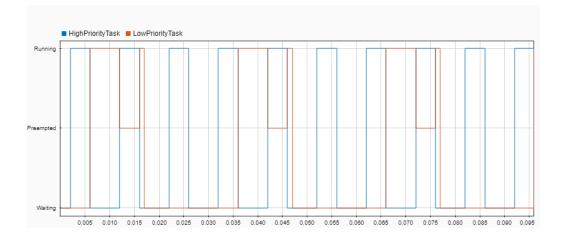

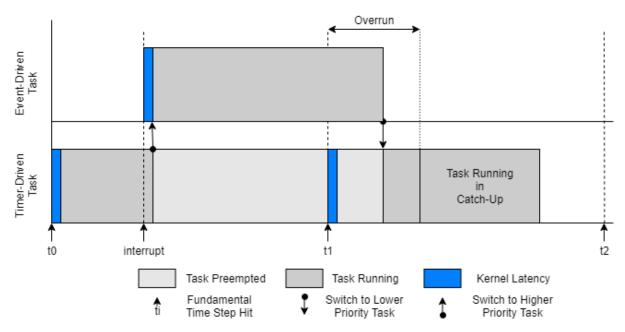

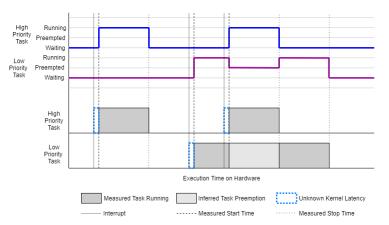

SoC Blockset models simulate *Kernel latency* as a delay at the start of execution of a task the first time the task moves from the waiting to running state. The following diagram shows the execution timing of a high-priority and low-priority task on a system that simulates a single processor core.

Other factors affecting kernel latency, such as context switch times, can be considered negligible compared to other effects and are not modeled in simulation.

**Note** Kernel latency requires advanced knowledge of the processor specifications and can be generally set to 0 without impact to the simulation.

## **Effect Kernel Latency on Task Execution**

This example shows the effect of kernel latency on the behavior and timing of two timer driven tasks in an SoC application.

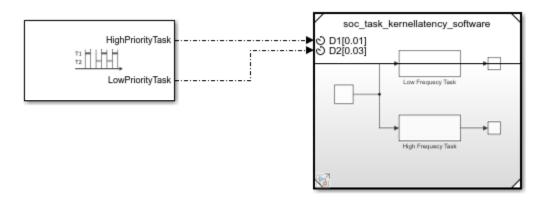

The following model simulates a software application with two timer driven tasks. The task characteristics, specified in the Task Manager block, are as follows:

| Name             | Period | Mean Duration |

|------------------|--------|---------------|

| HighPriorityTask | 0.01   | 0.004         |

| LowPriorityTask  | 0.03   | 0.007         |

With these timing conditions, the high priority task preempts the low priority task. In the model Configuration Parameters dialog box, the **Hardware Implementation > Operating system/scheduler > Kernel latency** is set to 0.002.

Run the model and open the Simulation Data Inspector (SDI) display. Selecting the two task signal produces the following display.

Inspecting the SDI display, a change in task state state from *Waiting* to *Running* shows a latency of 0.002 seconds. However, when the task changes from *Preempted* to *Running*, no latency occurs. This timing matches with the expected behavior of task, experiencing a latency in startup of that task execution instance, but not when the task instance already exists.

# See Also

Task Manager

## **More About**

- "What is Task Execution?" on page 1-2

- "Task Duration" on page 1-14

# **Task Duration**

The total time an instance of a task spends in the running state defines the task duration. Task duration can vary due to multiple sources, in particular:

- Conditional branching in the task algorithm

- Dependence on signal values from other tasks

- Dependence on signals from external sources, such as I/O devices or hardware user logic

- Compiler settings and SoC device processor architecture

As a result, task duration for any given task instance can be nondeterministic.

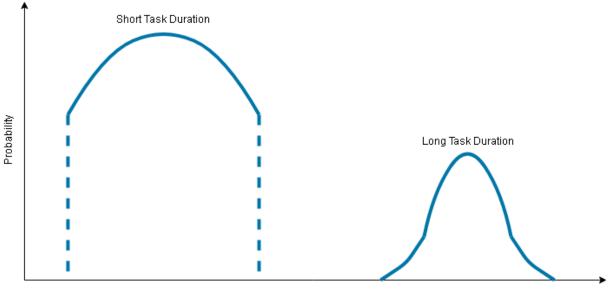

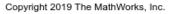

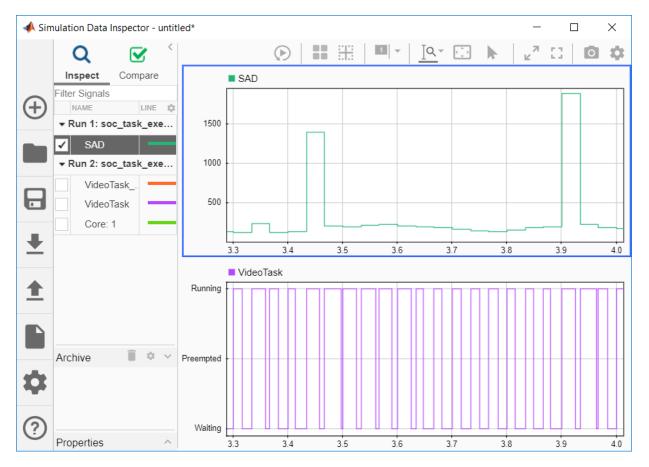

The Task Manager block provides four ways to simulate the nondeterministic task duration: approximation using a parameterized probability distribution, approximation using a calculated probability distribution, and replay of recorded task execution timing data.

## **Approximation Using Parameterized Probability Distribution**

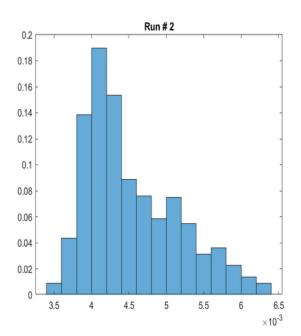

In simulation, the Task Manager block can define the task duration as random variable expressed as the weighted sum of truncated normal distributions. For example, this diagram shows the probability distribution of a task that executes with a short task duration, but can occasionally execute with a longer durations.

Execution Time

To create a probability distribution for a task duration, first open the Task Manager block dialog. Then, on the **Simulation** tab, set **Specify task duration via:** to Dialog. In the **Task duration settings** section, you can set the properties of each distribution by editing the text of that property. You can also add and delete probability distributions from the sum of distributions by clicking the **Add distribution** and **Delete distribution** buttons, respectively.

-Task duration settings

Define probability distribution of the task duration times as a combination of up to five normal distributions, each with the specified occurrence probability.

|   | Percent | Mean  | SD    | Min   | Max   |

|---|---------|-------|-------|-------|-------|

| 1 | 70      | 1e-06 | 0     | 1e-06 | 1e-06 |

| 2 | 10      | 4e-06 | 1e-07 | 4e-06 | 5e-06 |

| 3 | 20      | 5e-06 | 1e-06 | 4e-06 | 6e-06 |

|   |         |       |       |       |       |

|   |         |       |       |       |       |

#### Note

- The sum of the Percent weights must equal 100.

- Each task can use a maximum of 5 distributions.

#### **Approximation Using Calculated Probability Distribution**

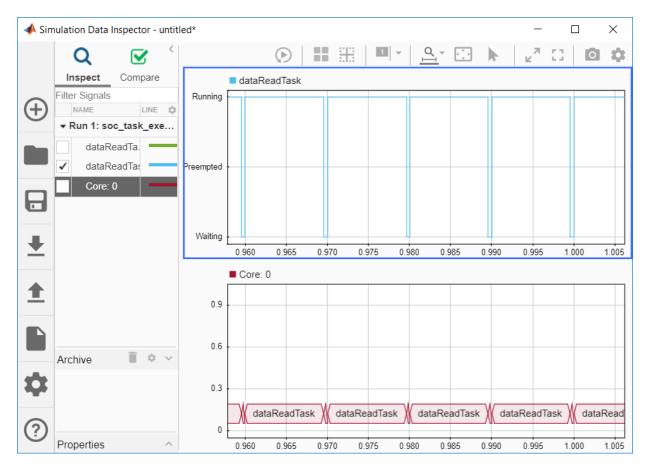

Each recording of task execution data, either from a previous simulation or from execution on an SoC device, generates several profiling files. The metadata.csv file contains the calculated mean and standard deviation for each task in that recording. To configure a task in the Task Manager block to use the derived statistical data for task duration, follow these steps:

- **1** Open the Task Manager block dialog mask.

- 2 On the **Simulation** tab, set **Specify task duration via** to Recorded task diagnostics file.

- **3** Specify the location and name of the metadata.csv file. The Mean and Deviation parameters are automatically updated with the data from the file.

- 4 Click OK.

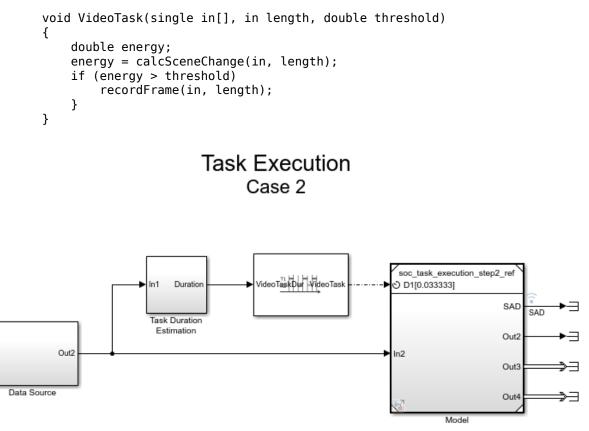

### **Specification from Task Manager Input Port**

An input port on the Task Manager block dynamically specifies the task duration. To expose this task duration input port, follow these steps:

- **1** Open the Task Manager block dialog mask.

- 2 On the Simulation tab, set Specify task duration via to Input port.

- 3 Click **OK** to expose a new input port, named **TaskNameDur**, on the block.

## **Replay of Recorded Task Execution Timing Data**

A data file provides exact task duration for each task execution instance. A task execution data file can come from a previous or independent model simulation or directly from the task execution on a processor in an SoC device. For more information on replaying recorded task execution timing data, see "Task Execution Playback using Recorded Data" on page 2-9.

# See Also

Task Manager

## More About

- "What is Task Execution?" on page 1-2

- "Task Execution Playback using Recorded Data" on page 2-9

## **External Websites**

Truncated Normal Distribution

# Value and Caching of Task Subsystem Signals

In SoC Blockset, a task subsystem can be treated as an independent model with the task duration simulating the expected execution time on an SoC device. When the Task Manager block executes a task, input signals connected to that task subsystem can either be sampled and cached at the start of the task execution or sampled at the end of the task execution instance. The task subsystem then executes using either the cached or latest value. The value of signals and buses output from the subsystem change at the end of the task execution instance.

To enable task subsystem input signal caching, first open the Simulink configuration parameters on the processor reference model. On the **Hardware Implementation** pane, select **Hardware board settings > Task and memory simulation > Cache input data at task start**.

## See Also

Task Manager

#### **More About**

- "What is Task Execution?" on page 1-2

- "Task Duration" on page 1-14

- "Kernel Latency" on page 1-11

# Memory and Register Data Transfers

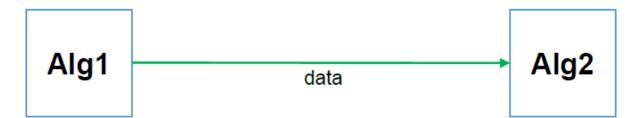

An SoC application is composed of one or more algorithms. When an algorithm transfers data to another algorithm, the data is represented as a signal line in Simulink. For behavioral models, the data transfer is instantaneous.

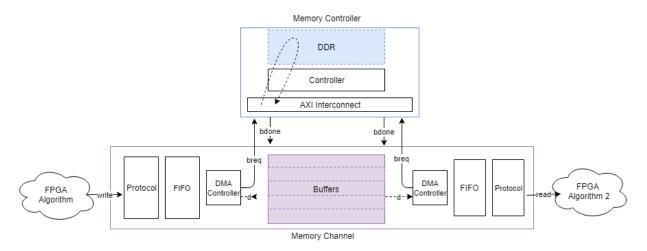

This diagram shows a behavioral model of a datapath between two algorithms.

In the physical world, the algorithms can be on two separate devices, and data transfers do not happen instantaneously. Furthermore, the algorithms can run at different rates, and therefore require buffering and control logic for handshaking. For example, a simple handshake such as "data is valid" from the producer of the data and "ready to accept data" from the consumer serve as control logic.

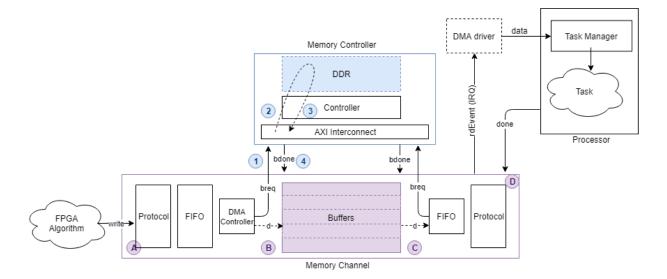

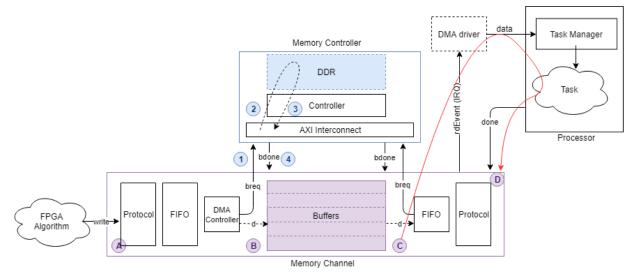

If one processing element executes in an FPGA or ASIC, and the next processing element executes on an embedded processor, then a simple signal line represents more than just a complex hardware datapath. The data transfer also represents a processor interrupt handler, an operating system task scheduler, and a software driver stack.

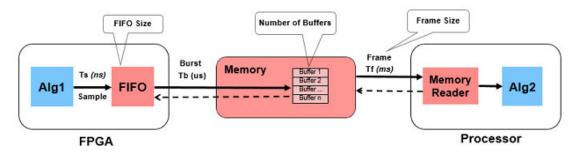

In SoC Blockset, you model data transfers and handshake protocols through shared memory. Use a Memory Channel block for external memory or a Register Channel block for registers.

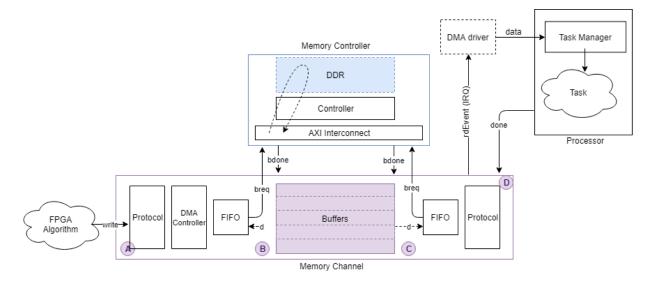

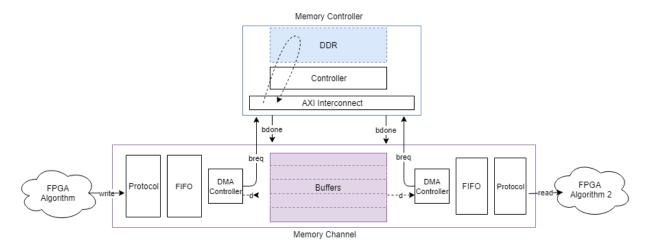

## **Modeling Datapath with Memory Channel Block**

The Memory Channel block represents an abstraction to a complex datapath through external memory and supports different handshake protocols. It facilitates a refinement of the communication between processing elements from an instantaneous, protocol-less wire to a full direct memory access (DMA) connection between a processor and an FPGA.

By adding a Memory Channel block, you can model data movement from one part of the algorithm to another.

The block provides a model of the communication pipeline. The channel also provides a signaling interface.

The interface protocol depends on where the processing is executed. An FPGA or ASIC algorithm can perform data transfers by using standard protocols such as AXI4-Stream or AXI4. An embedded CPU algorithm can use a driver-interface exported to the user space.

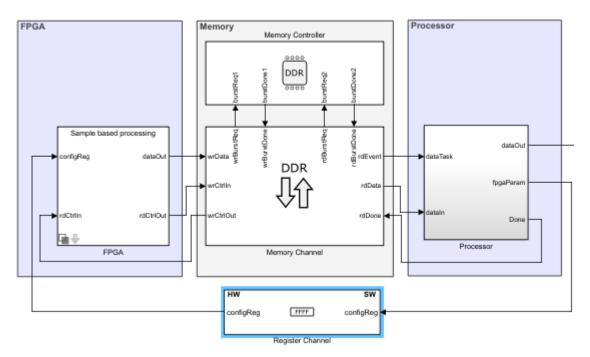

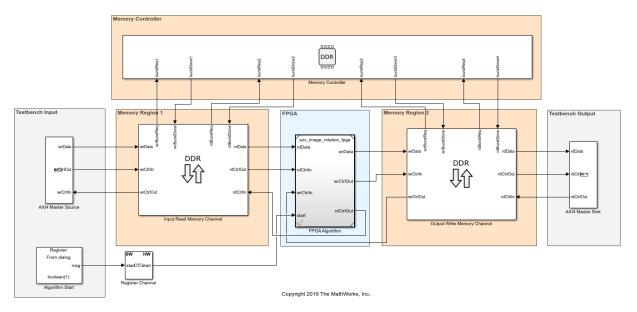

This figure shows a model of the datapath from an FPGA algorithm streaming data to a processor algorithm.

Other Memory Channel type selections model additional common datapaths through external memory. For more information about Memory Channel configurations, see Memory Channel.

The writer and reader are connected to the memory and request access to the external memory from a memory controller. For more information about the Memory Controller block, see Memory Controller.

## **Modeling Datapath with Register Channel Block**

The Register Channel block represents the serialization of the processor reads or writes through a common configuration bus such as AXI-Lite.

The Register Channel block provides a timing model for the transfer of register values between processor and hardware algorithms through a common configuration bus. Use this block when the processor writes a command or configuration register or when the processor reads a status register.

# See Also

Memory Channel | Register Channel

## **More About**

• "External Memory Channel Protocols" on page 2-41

# **Simplified AXI4 Master Interface**

#### In this section...

"Simplified AXI4 Master Protocol - Write Channel" on page 1-23 "Simplified AXI4 Master Protocol - Read Channel" on page 1-25

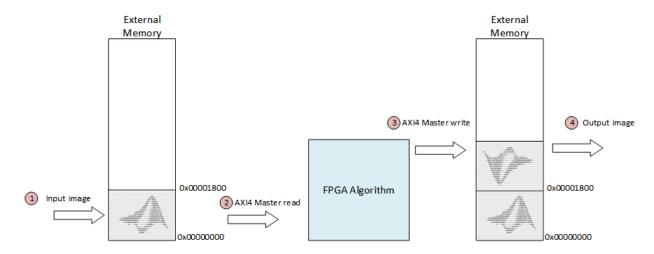

For designs that require accessing large data sets from an external memory, model your algorithm with a simplified AXI4 Master protocol. When you run the **IP** Core Generation workflow, HDL Coder<sup>™</sup> generates an IP core with AXI4 Master interfaces. The AXI4 Master interface can communicate between your design and the external memory controller IP by using the AXI4 Master protocol.

### **Simplified AXI4 Master Protocol - Write Channel**

You can use the simplified AXI4 Master protocol to map to AXI4 Master interfaces. Use the simplified AXI4 Master write protocol for a write transaction and the simplified AXI4 Master read protocol for a read transaction.

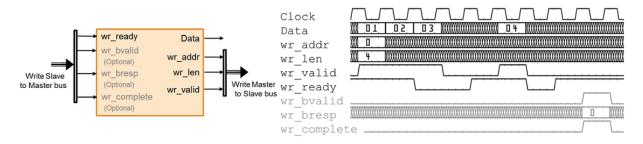

This figure shows the timing diagram for the signals that you model at the DUT input and output interfaces for an AXI4 Master write transaction.

The DUT waits for wr\_ready to become high to initiate a write request. When wr\_ready becomes high, the DUT can send out the write request. The write request consists of the Data and Write Master to Slave bus signals. This bus consists of wr\_len, wr\_addr, and wr\_valid. wr\_addr specifies the starting address that DUT wants to write to. The wr\_len signal corresponds to the number of data elements in this write transaction. Data can be sent as long as wr\_valid is high. When wr\_ready becomes low, the DUT must stop sending data within one clock cycle, and the Data signal becomes invalid. If the DUT continues to send data after one clock cycle, the data is ignored.

#### **Output Signals**

Model the Data and Write Master to Slave bus signals at the DUT output interface.

- Data: The data that you want to transfer, valid each cycle of the transaction.

- Write Master to Slave bus that consists of:

- wr\_addr: Starting address of the write transaction that is sampled at the first cycle of the transaction.

- wr\_len: The number of data values that you want to transfer, sampled at the first cycle of the transaction.

- wr\_valid: When this control signal becomes high, it indicates that the Data signal sampled at the output is valid.

#### **Input Signals**

Model the Write Slave to Master bus that consists of:

- wr\_ready: This signal corresponds to the backpressure from the slave IP core or external memory. When this control signal goes high, it indicates that data can be sent. When wr\_ready is low, the DUT must stop sending data within one clock cycle. You can also use the wr\_ready signal to determine whether the DUT can send a second burst signal immediately after the first burst signal has been sent. Multiple burst signals are supported, which means that the wr\_ready signal remains high to accept the second burst immediately after the last element of the first burst has been accepted.

- wr\_bvalid (optional signal): Response signal from the slave IP core that you can use for diagnosis purposes. The wr\_bvalid signal becomes high after the AXI4 interconnect accepts each burst transaction. If wr\_len is greater than 256, the AXI4 Master write module splits the large burst signal into 256-sized bursts. wr\_bvalid becomes high for each 256-sized burst.

- wr\_bresp (optional signal): Response signal from the slave IP core that you can use for diagnosis purposes. Use this signal with the wr\_bvalid signal.

- wr\_complete (optional signal): Control signal that when remains high for one clock cycle indicates that the write transaction has completed. This signal asserts at the last wr\_bvalid of the burst.

#### **Simplified AXI4 Master Protocol - Read Channel**

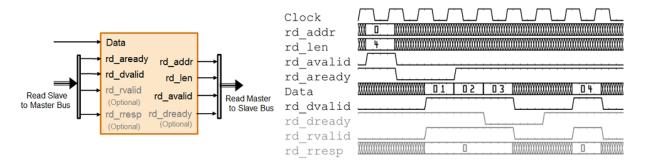

This figure shows the timing diagram for the signals that you model at the DUT input and output interfaces for an AXI4 Master read transaction. These signals include the Data, Read Master to Slave Bus, and Read Slave to Master Bus.

The DUT waits for rd\_aready to become high to initiate a read request. When rd\_aready is high, the DUT can send out the read request. The read request consists of the rd\_addr, rd\_len, and rd\_avalid signals of the Read Master to Slave bus. The slave IP or the external memory responds to the read request by sending the Data at each clock cycle. The rd\_len signal corresponds to the number of data values to read. The DUT can receive Data as long as rd dvalid is high.

#### **Read Request**

To model a read request, at the DUT output interface, model the Read Master to Slave bus that consists of:

- rd\_addr: Starting address for the read transaction that is sampled at the first cycle of the transaction.

- rd\_len: The number of data values that you want to read, sampled at the first cycle of the transaction.

- rd\_avalid: Control signal that specifies whether the read request is valid.

At the DUT input interface, implement the rd\_aready signal. This signal is part of the Read Slave to Master bus and indicates when to accept read requests. You can monitor the rd\_aready signal to determine whether the DUT can send consecutive burst requests. When rd\_aready becomes high, it indicates that the DUT can send a read request in the next clock cycle.

#### **Read Response**

At the DUT input interface, model the Data and Read Slave to Master bus signals.

- Data: The data that is returned from the read request.

- Read Master to Slave bus that consists of:

- rd\_dvalid: Control signal which indicates that the Data returned from the read request is valid.

- rd\_rvalid (optional signal): response signal from the slave IP core that you can use for diagnosis purposes.

- rd\_rresp (optional signal): Response signal from the slave IP core that indicates the status of the read transaction.

At the DUT output interface, you can optionally implement the rd\_dready signal. This signal is part of the Read Master to Slave bus and indicates when the DUT can start accepting data. By default, if you do not map this signal to the AXI4 Master read interface, the generated HDL IP core ties rd\_dready to logic high.

# **AXI4-Stream Interface**

Using SoC Blockset, you can model a simplified, streaming protocol in your model. Use HDL Coder to generate AXI4-Stream interfaces in the IP core.

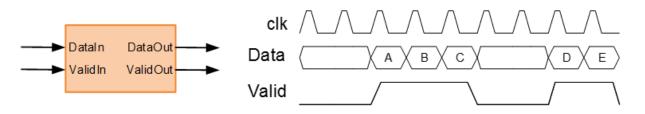

#### **Simplified Streaming Protocol**

When you want to generate an AXI4-Stream interface in your IP core, in your DUT interface, implement the following signals:

- Data

- Valid

When you map scalar DUT ports to an AXI4-Stream interface, you can optionally model the following signals and map them to the AXI4-Stream interface:

- Ready

- Other protocol signals, such as:

- TSTRB

- TKEEP

- TLAST

- TID

- TDEST

- TUSER

#### **Data and Valid Signals**

When the Data signal is valid, the Valid signal is asserted.

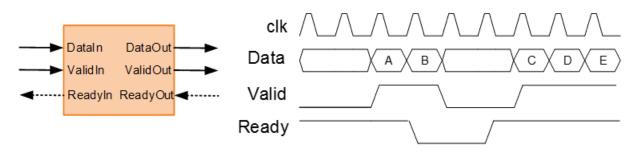

## **Ready Signal (Optional)**

The AXI4-Stream interfaces in your DUT can optionally include a Ready signal. In a Slave interface, the Ready signal enables you to apply back pressure. In a Master interface, the Ready signal enables you to respond to back pressure.

If you model the Ready signal in your AXI4-Stream interfaces, your Master interface ignores the Data and Valid signals one clock cycle after the Ready signal is deasserted. You can start sending Data and Valid signals once the Ready signal is asserted. You can send one more Data and Valid signal after the Ready signal is deasserted.

If you do not model the Ready signal, HDL Coder generates the signal and the associated back pressure logic.

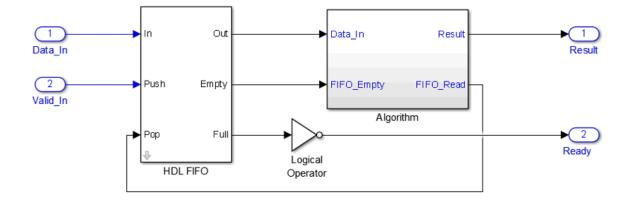

For example, if you have a FIFO in your DUT to store a frame of data, to apply back pressure to the upstream component, you can model the Ready signal based on the FIFO Full signal.

## **AXI4-Stream Video Interface**

#### In this section...

"Streaming Pixel Protocol" on page 1-30

"Protocol Signals and Timing Diagrams" on page 1-31

Using SoC Blockset, you can implement a simplified, streaming pixel protocol in your model. Use HDL Coder to generate an HDL IP core with AXI4-Stream Video interfaces.

### **Streaming Pixel Protocol**

You can use the streaming pixel protocol for AXI4-Stream Video interface mapping. Video algorithms process data serially and generate video data as a serial stream of pixel data and control signals.

To generate an IP core with AXI4-Stream Video interfaces, in your DUT interface, implement these signals:

- Pixel Data

- Pixel Control Bus

The **Pixel Control Bus** is a bus that has these signals:

- hStart

- hEnd

- vStart

- vEnd

- valid

The signals **hStart** and **hEnd** represent the start of an active line and the end of an active line respectively. The signals **vStart** and **vEnd** represent the start of a frame and the end of a frame.

You can optionally model the backpressure signal, **Ready**, and map it to the AXI4-Stream Video interface.

## **Protocol Signals and Timing Diagrams**

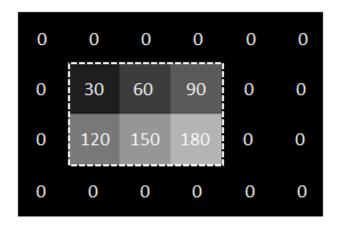

This figure is a 2-by-3 pixel image. The active image area is the rectangle with a dashed line around it and the inactive pixels that surround it. The pixels are labeled with their grayscale values.

#### **Pixel Data and Pixel Control Bus**

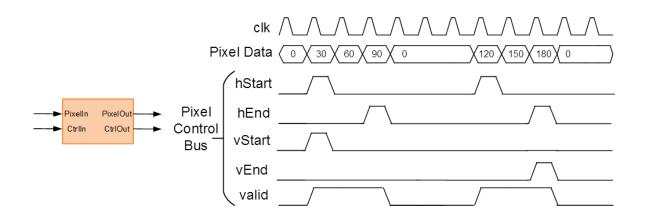

This figure shows the timing diagram for the **Pixel Data** and **Pixel Control Bus** signals that you model at the DUT interface.

The **Pixel Data** signal is the primary video signal that is transferred across the AXI4-Stream Video interface. When the **Pixel Data** signal is valid, the **valid** signal is asserted.

The **hStart** signal becomes high at the start of the active lines. The **hEnd** signal becomes high at the end of the active lines.

The **vStart** signal becomes high at the start of the active frame in the second line. The **vEnd** signal becomes high at the end of the active frame in the third line.

#### **Optional Ready Signal**

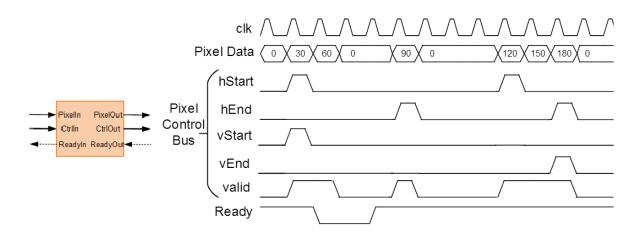

This figure shows the timing diagram for the **Pixel Data**, the **Pixel Control Bus**, and the **Ready** signal that you model at the DUT interface.

When you map the DUT ports to an AXI4-Stream Video interface, you can optionally model the backpressure signal, **Ready**, and map it to the AXI4-Stream Video interface.

In a Slave interface, with the **Ready** signal, you can apply back pressure. In a Master interface, with the **Ready** signal, you can respond to back pressure.

If you model the **Ready** signal in your AXI4-Stream Video interfaces, your Master interface must deassert its **valid** signal one cycle after the **Ready** signal is deasserted.

If you do not model the  ${\bf Ready}$  signal, HDL Coder generates the associated backpressure logic.

# Models with I/O Device Blocks

The **Processor I/O** sublibrary in the SoC Blockset contains blocks that simulate the data transfer between the processor system and other I/O devices in the SoC application. **Processor I/O** blocks, including the Register Read, Register Write, and Stream Read, can read and write data to internal I/O, such as DDR memory or registers, on the SoC device. Similarly, the TCP Read, TCP Write, UDP Read, and UDP Write blocks can read and write data to external communication I/O devices.

### **Processor I/O with Memory Model**

**Processor I/O** blocks, including the Register Read, Register Write, and Stream Read, simulate reading and writing of data to registers and shared memory.

### **Processor I/O with Network Device Model**

**Processor I/O** blocks, including the TCP Read, TCP Write, UDP Read, and UDP Write blocks, simulate the exchange of data to external communication protocols supported by an SoC device.

# See Also

## **Use Template to Create SoC Model**

SoC Blockset model templates provide design patterns and best practices for models intended for simulation, HDL code generation, or SoC deployment. Models created from any one of SoC Blockset model templates have their configuration parameters set up for simulation and code generation.

### **Create SoC Model Using SoC Blockset Template**

To efficiently model hardware for SoC design, create a project by using an SoC Blockset template.

1 In the MATLAB<sup>®</sup> Home tab, select the **Simulink** button. Alternatively, at the command line, enter:

simulink

- **2** On the Simulink Start Page, scroll down to the **SoC Blockset** section, which contains links to SoC templates for common workflows. Select a template and save the project. A project folder opens in your workspace containing:

- A model with the name soc\_\*\_top.slx The top-level model for the SoC project.

- referencedmodels A folder containing the models referenced from the top model. Some templates include an FPGA model and a processor model. Other templates only include one referenced model: an FPGA model or a processor model.

- utilities A folder containing utility functions or testbench data used by the model.

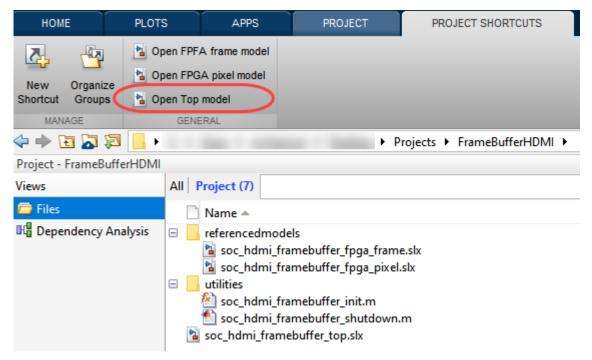

To open the top-level model in Simulink, on the **Project Shortcuts** tab, click **Open Top model**.

**3** In each template, navigate to the blocks marked **FPGA Algorithm** in the FPGA model, or **Processor Algorithm** in the processor model. These blocks are highlighted for easy detection. Replace the template blocks with your own algorithm model.

**Tip** To easily find the algorithm blocks, follow the annotations throughout the model hierarchy.

4 To open the **SoC Blockset** Block Library, select the Library Browser button, then select **SoC Blockset** in the left pane. Alternatively, at the command line, enter:

soclib

This library includes blocks for creating SoC models and testbenches.

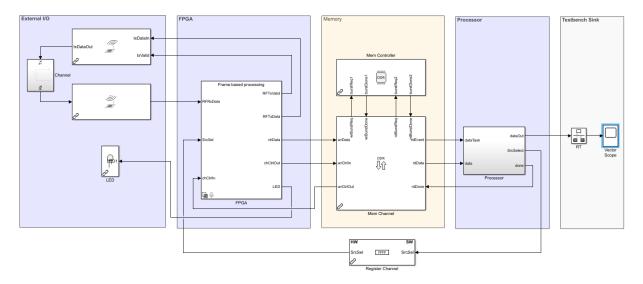

## **Template Structure**

The top model in an SoC Blockset template includes an FPGA subsystem, which represents the logic intended to program the FPGA. The FPGA subsystem includes two Simulink model variants:

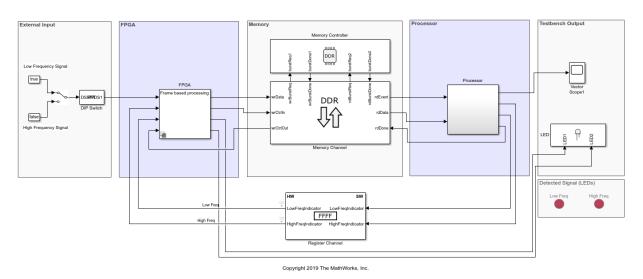

- Frame-based FPGA model For enhanced simulation performance

- Sample-based FPGA model For cycle accuracy and code generation

The top model also includes a processor subsystem, which represents the software program intended to run on the SoC processor. Both the FPGA and the top subsystems contain blocks marked as FPGA Algorithm or Processor Algorithm. Replace these algorithms with your own logic. The top model of the template also includes a memory system, with a memory controller and memory channels. These blocks represent the physical memory system on the board. The model often includes a register channel (to enable communication between the processor and FPGA), testbench, or I/O blocks.

## **Modify Project**

#### Modify the FPGA Model

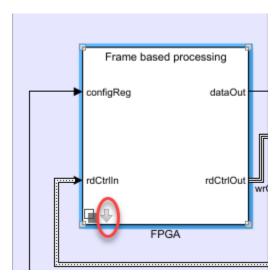

From the top model, open the FPGA model by clicking the arrow at the bottom left of the FPGA block:

The FPGA model contains two model variants: a frame-based variant and a sample-based variant. Double-click the model variant you want to modify. The FPGA model typically includes two main subsystems for you to modify:

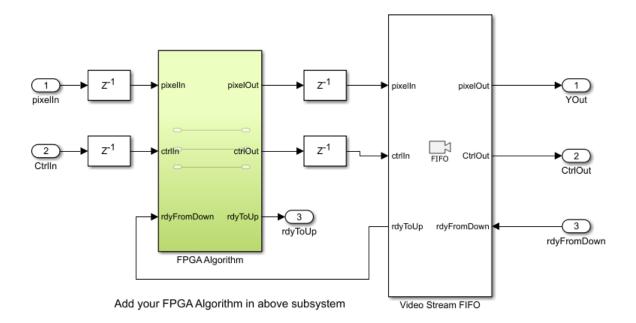

- FPGA Algorithm Wrapper Double-click to open the model. The algorithm wrapper contains a green-highlighted subsystem named FPGA Algorithm. This block has two inputs and one output and is implemented as a multiplier. Replace this block with your own FPGA algorithm. Add inputs and outputs as required.

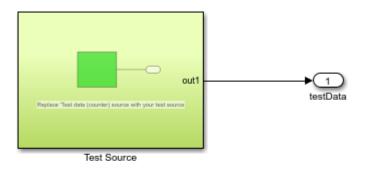

- Test Source Wrapper This block includes a test source and is intended to generate stimulus as an input to the FPGA algorithm. Modify the test source to your needs, or replace it with an alternative source block. If the input to your FPGA algorithm is routed from an I/O block, such as HDMI or SDR, consider using a specific application template.

**Note** Not all templates include a Test Source block in the FPGA model.

#### **Modify the Processor Model**

The processor model includes a Task Manager block and a processor wrapper. The template implements the processor algorithm as a "pass through" wire. Open the processor algorithm wrapper, and replace the Processor Algorithm block (highlighted in blue) with your desired algorithm.

#### **Modify the Register Channel**

The top model of a template also includes a register channel to communicate between the processor and the FPGA model. Use the register channel to configure the FPGA mode, lor to read and check status registers. The Register Channel block in the template includes one register. To add additional registers you must modify the register channel block parameters, the FPGA algorithm, and the processor algorithm:

- 1 Add registers to the register channel Double-click the Register Channel block to open the block mask and add additional registers as needed. Adding registers creates additional ports on the Register Channel block. For additional information, see Register Channel.

- 2 Add ports to the processor model Navigate to the Processor Algorithm Wrapper model. To navigate to the processor model, click **Open Processor model** on the **Project Shortcuts** tab. Double-click Processor Algorithm Wrapper to modify it.

For write registers, add an output port to the module and add logic to drive a value to the added output port. For read registers, add an input port and logic to process the

information returned from a read register. From the top model, wire the port to the Register Channel block.

3 Add ports to the FPGA model - Navigate to the FPGA Algorithm Wrapper model. To navigate to the FPGA/Frame based processing model, click **Open FPGA sample model** on the **Project Shortcuts** tab. Double-click FPGA Algorithm Wrapper to modify it.

For write registers, add an input port to the module and logic to process the information returned from a read register. For read registers, add an output port and logic to drive a value to the added output port.

For equivalent behavior when using a Simulink sample-based variant, repeat this step for the sample-based processing model in the FPGA wrapper.

4 From the top model, wire the new port to the Register Channel block.

## See Also

Memory Controller | Memory Channel | Register Channel | Task Manager

### **More About**

- "Stream from FPGA to Processor Template" on page 1-47

- "SDR Template" on page 1-51

- "HDMI Template" on page 1-40

- "Frame Buffer with HDMI Template" on page 1-43

# **HDMI** Template

The High-Definition Multimedia Interface (HDMI) template provides a simulation model for SoC video streaming using SoC Blockset Support Package for Xilinx® Devices. Use this template to simulate and analyze the effects of internal and external connectivity, such as HDMI I/O behavior on a vision processing algorithm.

## **Required Products**

- Computer Vision Toolbox<sup>™</sup>

- Vision HDL Toolbox<sup>™</sup>

- SoC Blockset Support Package for Xilinx Devices

### **Template Structure**

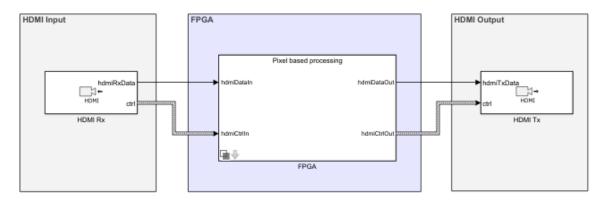

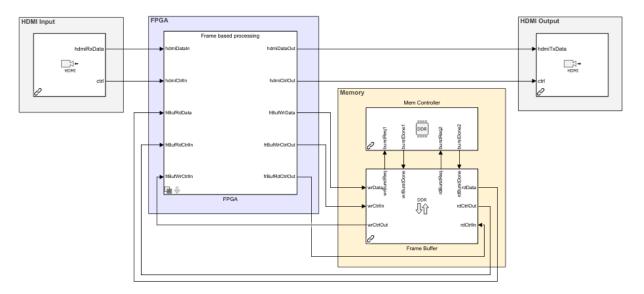

HDMI video streams from an HDMI Rx block into the FPGA, which implements a video data processing algorithm. The processed images stream to the HDMI Tx block.

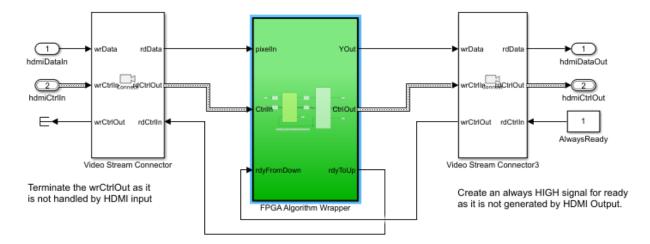

FPGA pixel model uses Video Stream Connector blocks to connect different subsystems and to connect to the HDMI I/O blocks. VideoStream Connector required to be able to generate each subsystem as a separate IP in the implemented reference design from the model. Since the FPGA frame model is for simulation purposes only and is not used for implementation, the Video stream connector blocks are not modeled.

## **Modify Project**

In MATLAB, on the **Project Shortcuts** tab, click **Open FPGA pixel model**. Open the FPGA Algorithm Wrapper, as shown highlighted in green.

The FPGA Algorithm, also highlighted in green, contains feedthrough ports and signals.

You can modify the content of the FPGA algorithm model to incorporate your desired vision processing algorithm, with complete simulation and code generation of the surrounding video memory system. For pure algorithm design and investigation, click **Open FPGA frame model** in the **Project Shortcuts** tab, and repeat this step.

# See Also

"Use Template to Create SoC Model" on page 1-35 | "Create a New Project Using Templates" (Simulink)

## **More About**

• "What Are Projects?" (Simulink)

# Frame Buffer with HDMI Template

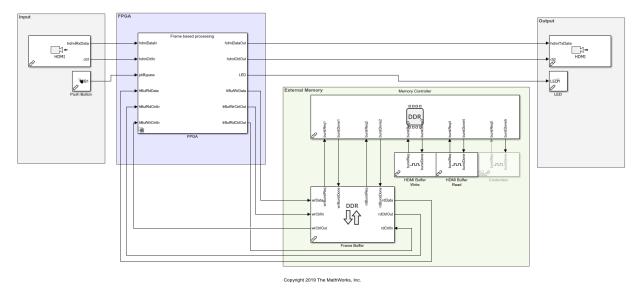

The Frame Buffer with High-Definition Multimedia Interface (HDMI) template creates a Simulink project with models to simulate and generate a video application with external memory frame buffer. This template forms the base for the "Histogram Equalization Using Video Frame Buffer" on page 5-24 example. Use this template to simulate the full reference design of a video processing application on an FPGA with HDMI I/O and connection to an external memory frame buffer for advanced image processing designs.

## **Required Products**

- Vision HDL Toolbox

- Computer Vision Toolbox

- SoC Blockset Support Package for Xilinx Devices

### **Template Structure**

HDMI video streams video data from an HDMI Rx block into the FPGA. The FPGA implements a color-space transformation and your image processing algorithm. The processed images then undergo the inverse color-space transformation and stream to the

HDMI Tx block. The FPGA algorithm is connected to the external memory frame buffer Memory Channel block configured in ALI-Stream Video Frame Buffer mode.

The FPGA pixel model uses Video Stream Connector blocks to connect different subsystems and to connect to HDMI I/O blocks. This is required to be able to generate each subsystem as a separate IP in the implemented reference design from the model. Since the FPGA frame model is for simulation purposes only and is not used for implementation, the Video Stream Connector blocks are not modeled.

### **Modify Project**

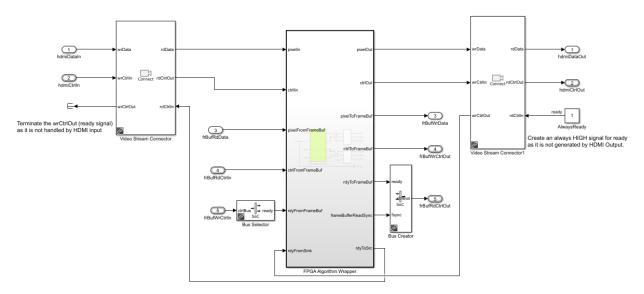

In MATLAB, on the **Project Shortcuts** tab, click **Open FPGA pixel model**. Double-click to open the FPGA Algorithm Wrapper.

Modify the content of the FPGA Algorithm subsystem to incorporate your desired vision processing algorithm, with complete simulation and code generation of the surrounding video memory system. The **pixelToFrameBuf** and **pixelFromFrameBuf** ports provide access to the external memory channel, Frame Buffer. For pure algorithm design and investigation, in the **Project Shortcuts** tab, click **Open FPGA frame model**, and repeat this step.

## See Also

"Use Template to Create SoC Model" on page 1-35 | "Create a New Project Using Templates" (Simulink)

### **More About**

• "What Are Projects?" (Simulink)

• "Histogram Equalization Using Video Frame Buffer" on page 5-24

## **Stream from FPGA to Processor Template**

Use the *Stream from FPGA to Processor* template to create an SoC Blockset model for designing a datapath from hardware (FPGA) to software (Processor). To create a project using the "Stream to Processor" template, follow the steps to "Create SoC Model Using SoC Blockset Template" on page 1-35.

## **Required Products**

For sample-based processing, no additional products are required.

For *frame-based* processing, DSP System Toolbox<sup>™</sup> is required.

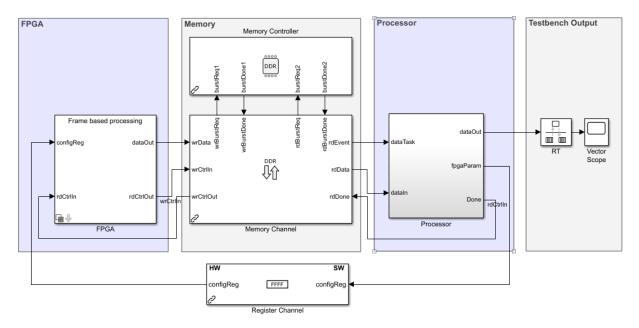

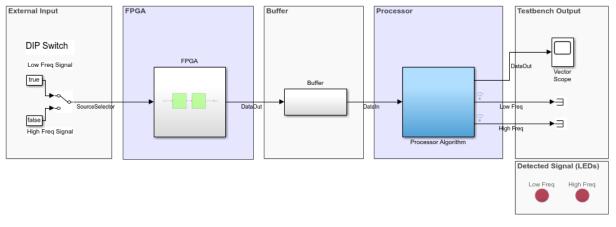

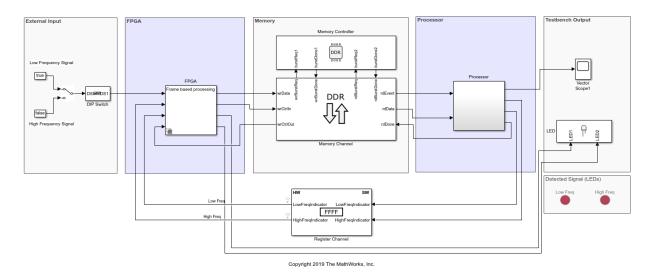

## **Template Structure**

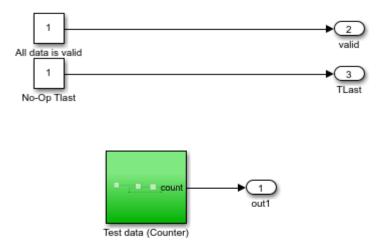

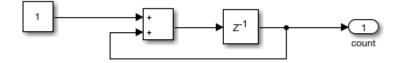

This template models a counter as the test data source and minimal logic for the FPGA and processor algorithms. Use this template as a guide and replace the FPGA algorithm and Processor algorithm with your own functionality. The FPGA algorithm is a simple multiplication performed on input data from the test source and from a **configReg**

parameter. The processor writes the **configReg**. This parameter is modeled using the Register Channel block. Data from the FPGA algorithm is passed to the processor through a Memory Channel block. The memory **Channel Type** parameter is set to AXI4-Stream to Software via DMA, which models the DMA data transfer through shared external memory.

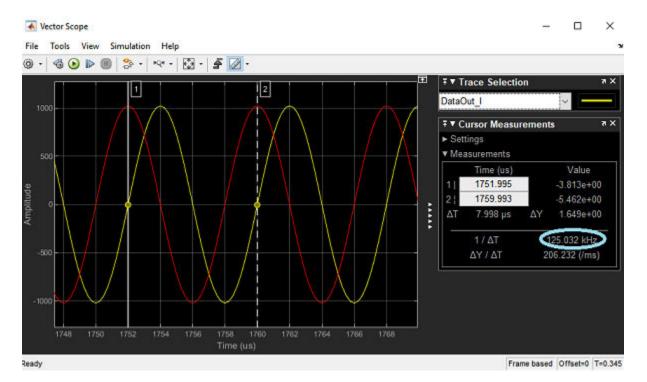

The processor reads the computed data from the memory and performs additional computing, which is implemented in the template as a pass-through wire. You can view the simulation results by double-clicking the Vector Scope block in the testbench sink.

## **Modify Project**

#### **Modify the FPGA Model**

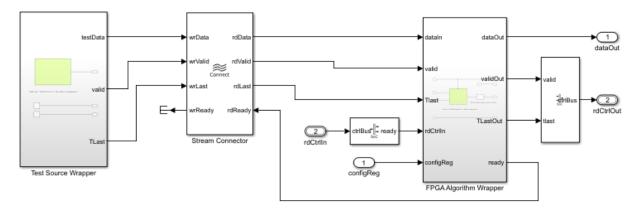

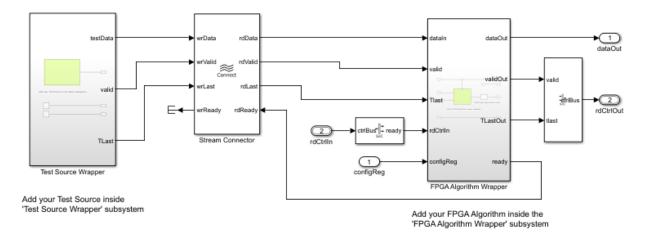

In the MATLAB toolstrip, on the **Project Shortcuts** tab, click **Open FPGA sample model** to open the FPGA model. In the model, two areas are highlighted green, which represents user code: one in the FPGA Algorithm Wrapper block and one in the Test Source Wrapper block.

- FPGA Algorithm Wrapper Double-click to open the model. The algorithm wrapper contains a green-highlighted subsystem named FPGA Algorithm. This block has two inputs and one output and is implemented as a multiplier. Replace this block with your own FPGA algorithm. Add inputs and outputs as required.

- Test Source Wrapper This block includes a test source and is intended to generate stimulus as an input to the FPGA algorithm. This block is implemented as a counter in this template. Modify the test source to your needs, or replace it with an alternative source block.

**Tip** When your FPGA model includes more than one IP, you must define each IP as a subsystem and connect the subsystems using a Stream Connector or Video Stream Connector block. For additional information, see "Considerations for Multiple IPs in FPGA Model" on page 1-56.

To enable consistent simulation behavior, click **Open FPGA frame model** in the **Project Shortcuts** tab and repeat this step. To simulate frame-based processing, you must have a DSP System Toolbox license.

#### **Modify the Processor Model**

In the MATLAB toolstrip, on the **Project Shortcuts** tab, click **Open Processor model**. The processor wrapper contains a blue highlighted subsystem representing the user code for the processor algorithm. Open the Processor Algorithm wrapper and replace the Processor Algorithm block with your desired algorithm.

#### Modify the Register Channel

The top model of a template also includes a register channel to communicate between the processor and the FPGA model. Use the register channel to configure the FPGA model, or to read and check status registers. The Register Channel block in the template includes one register. To add additional registers you must modify the register channel block parameters, the FPGA algorithm, and the processor algorithm:

- 1 Add registers to the register channel Double-click the Register Channel block to open the block mask and add additional registers as needed. Adding registers creates additional ports on the Register Channel block. For additional information, see Register Channel.

- 2 Add ports to the processor model Navigate to the Processor Algorithm Wrapper model. To navigate to the processor model, click **Open Processor model** on the **Project Shortcuts** tab. Double-click Processor Algorithm Wrapper to modify it.

For write registers, add an output port to the module and add logic to drive a value to the added output port. For read registers, add an input port and logic to process the information returned from a read register. From the top model, wire the port to the Register Channel block.

3 Add ports to the FPGA model - Navigate to the FPGA Algorithm Wrapper model. To navigate to the FPGA/Frame based processing model, click **Open FPGA sample model** on the **Project Shortcuts** tab. Double-click FPGA Algorithm Wrapper to modify it.

For write registers, add an input port to the module and logic to process the information returned from a read register. For read registers, add an output port and logic to drive a value to the added output port.

For equivalent behavior when using a Simulink sample-based variant, repeat this step for the sample-based processing model in the FPGA wrapper.

4 From the top model, wire the new port to the Register Channel block.

# See Also

#### **More About**

• "Use Template to Create SoC Model" on page 1-35

## **SDR Template**

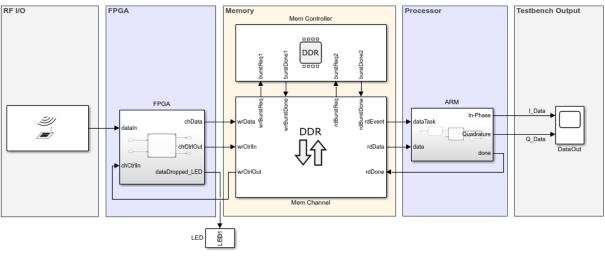

The software defined radio (SDR) template provides a simulation model for an SoC reference design available from Communications Toolbox<sup>™</sup> Support Package for Xilinx Zynq<sup>®</sup>-Based Radio. Use this template to simulate the full reference design and analyze the effects of internal and external connectivity on and SDR algorithm, such as memory behavior and Radio Frequency (RF) I/O behavior.

To get started with SoC Blockset model for designing an SDR system, follow the steps to "Create SoC Model Using SoC Blockset Template" on page 1-35.

### **Required Products**

- Communications Toolbox

- SoC Blockset Support Package for Xilinx Devices

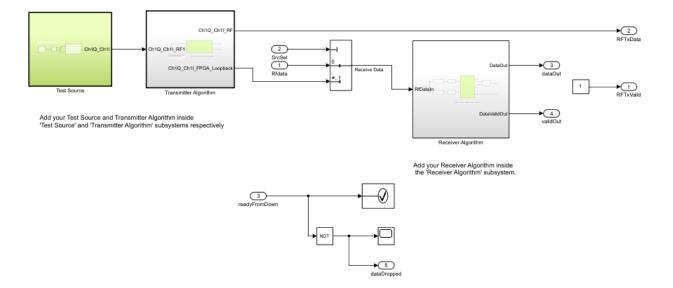

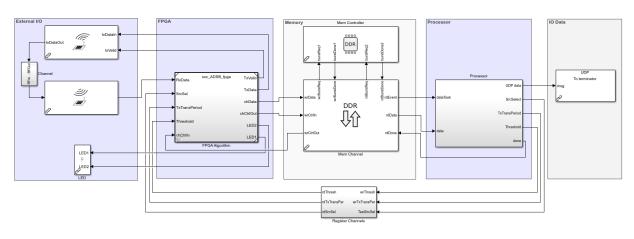

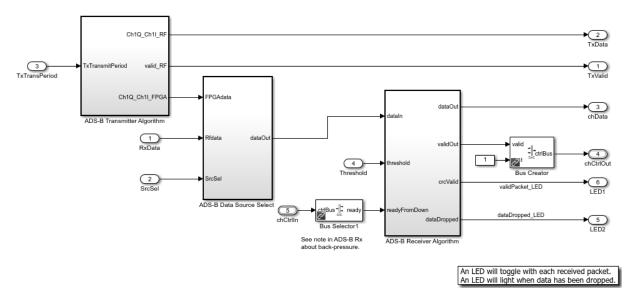

#### **Template Structure**

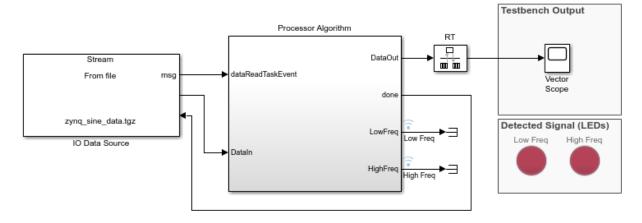

This template models an SDR transceiver composed of AD9361 transmitter and receiver blocks. The transceiver connects an RF channel to the FPGA, which implements a receiver and a transmitter algorithm. The FPGA algorithm includes a Test Source block,

which generates a sinusoid signal and drives it to the transmitter. The FPGA algorithm also includes a Tx algorithm, implemented as simple pass-through wires, and an Rx algorithm, implemented as a gain block. A configuration register **srcSel** is modeled in the FPGA to select the source of data for the Rx algorithm. The processor writes the **srcSel** register to select either the test source from the FPGA or RF data from the transceiver. This register is modeled using the Register Channel block. Data from the FPGA algorithm is passed to the processor through a Memory Channel block.

Use this template as a guide and replace the Rx Algorithm and Tx Algorithm in the FPGA and the Processor Algorithm in the processor with your own functionality. The memory **Channel Type** parameter is set to AXI4-Stream to software via DMA, which models the direct memory access (DMA) data transfer through shared external memory.

The processor reads the computed data from the memory, and performs additional computing (implemented in the template as a pass-through wire). You can view the simulation results by double-clicking the Vector Scope block in the testbench sink.

## **Modify Project**

#### **Modify the FPGA Model**

In MATLAB, on the **Project Shortcuts** tab, click **Open FPGA sample model**. Then, open the FPGA Transceiver Algorithm Wrapper. Notice three areas highlighted in green. These areas represent user code and are located in the Receiver Algorithm block, in the Transmitter Algorithm block, and the Test Source block.

The FPGA model includes the following sections for you to modify (highlighted in green):

- Test Source block This block generates a 10-kHz sinusoid signal and drives it to the transmitter algorithm. Modify the test source to your needs or replace it with an alternative source block.

- Receiver Algorithm subsystem Inside the green-highlighted subsystem named Rx Algorithm, there is a block labeled Algorithm. The algorithm takes I/Q data as input and output with a valid signal. Replace this block with your own Rx algorithm.

- Transmitter Algorithm Inside the green-highlighted subsystem named Tx Algorithm, the algorithm has an input from the test source and two output signals: one to the RF channel and one to the FPGA. Replace this block with your own Tx algorithm.

To enable consistent simulation behavior, in the **Project Shortcuts** tab, click **Open FPGA frame model** and repeat this step.

#### **Modify the Processor Model**

In MATLAB, on the **Project Shortcuts** tab, click **Open processor model**. The subsystem highlighted in blue represents the user code for the processor algorithm. Open the Processor Algorithm wrapper and replace the internal Processor Algorithm block (also highlighted in blue) with your desired algorithm.

#### **Modify the Register Channel**

The top model of a template also includes a register channel to communicate between the processor and the FPGA model. Use the register channel to configure the FPGA mode,l or to read and check status registers. The Register Channel block in the template includes one register. To add additional registers you must modify the register channel block parameters, the FPGA algorithm, and the processor algorithm:

- 1 Add registers to the register channel Double-click the Register Channel block to open the block mask and add additional registers as needed. Adding registers creates additional ports on the Register Channel block. For additional information, see Register Channel.

- 2 Add ports to the processor model Navigate to the Processor Algorithm Wrapper model. To navigate to the processor model, click **Open Processor model** on the **Project Shortcuts** tab. Double-click Processor Algorithm Wrapper to modify it.

For write registers, add an output port to the module and add logic to drive a value to the added output port. For read registers, add an input port and logic to process the information returned from a read register. From the top model, wire the port to the Register Channel block.

**3** Add ports to the FPGA model – Navigate to the FPGA Algorithm Wrapper model. To navigate to the FPGA/Frame based processing model, click **Open FPGA sample**

**model** on the **Project Shortcuts** tab. Double-click FPGA Algorithm Wrapper to modify it.

For write registers, add an input port to the module and logic to process the information returned from a read register. For read registers, add an output port and logic to drive a value to the added output port.

For equivalent behavior when using a Simulink sample-based variant, repeat this step for the sample-based processing model in the FPGA wrapper.

**4** From the top model, wire the new port to the Register Channel block.

# **Considerations for Multiple IPs in FPGA Model**

When your FPGA model includes more than one block for which you'd like to generate HDL using HDL Coder, you must use a connector model to connect your blocks.

For additional information, see Stream Connector and Video Stream Connector blocks.

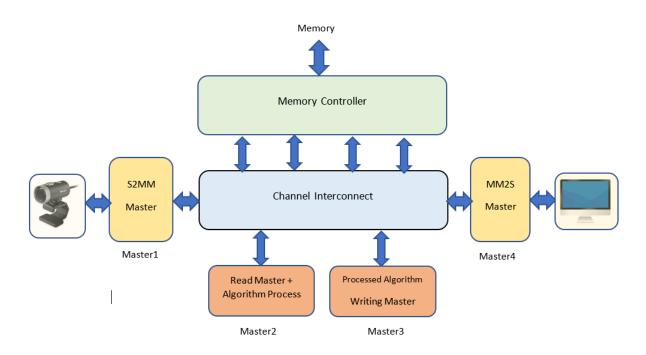

# **Create an SoC Project Application**

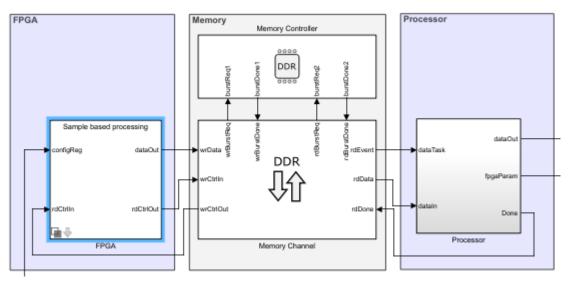

A system-on-chip (SoC) project developed using the SoC Blockset typically contains many diverse systems that make up a the complete application. These systems can include:

- Embedded processors with timer-driven and event-driven tasks.

- FPGAs with custom IP logic and timing.

- External memory systems with interaction to embedded processors and FPGAs.

- I/O device interaction, such as TCP/IP and UDP connections.

This example shows the steps to create an SoC application, using the features of the SoC Blockset, as a Simulink project. To begin, see "Project and Top-Level Model" on page 1-58.

**Note** This project is equivalent to the project automatically created by the "Stream from FPGA to Processor Template" on page 1-47. Templates are the recommended and preferred method for creating new projects. This example should be used for information purposes only.

# See Also

"Use Template to Create SoC Model" on page 1-35 | "Stream from FPGA to Processor Template" on page 1-47

# **Project and Top-Level Model**

An SoC application model developed using the SoC Blocksetcombines multiple subsystems and reference models. Each subsystem and reference model maps to a particular feature of an SoC device. Organization of the models and shared configuration settings requires a Simulink project.

- 1 Create a new SoC Blockset project named SampleSoCApplication. Creating a new project automatically creates a new project folder with the same name. For more information on creating projects, see "Create a New Project From a Folder" (Simulink).

- 2 Open a new Simulink model. Save the model as soc\_hwsw\_top.slx into the project folder.

- 3 Open the configuration parameters of the model. Select the Hardware Implementation tab and set the Hardware board to one of the supported boards for SoC Blockset, such as Xilinx Zynq ZC706 evaluation kit. Selecting the Hardware board automatically sets several parameters in the model related to that hardware board.

- 4 In the **Solver** tab, set **Solver selection** > **Type** to Variable-step.

- 5 Create three box areas and label them as FPGA, Memory, and Processor. For more information on creating box areas, see "Box and Label Areas of a Model" (Simulink). In the following sections, these areas are populated for various aspects of your SoC application.

6 Create a new MATLAB function to initialize variables used throughout the project.

```

function soc_hwsw_init

% Initialize the model wide variables and set them in base workspace.

SourceSTime = 1e-7;

FrameSize = 1000;

ProcSTime = SourceSTime*FrameSize;

FPGASTime = SourceSTime;

FPGAFrameSize = 1;

assignin('base','ProcSTime',ProcSTime);

assignin('base','FPGASTime',FPGASTime);

assignin('base','SourceSTime',SourceSTime);

assignin('base','FPGAFrameSize',FPGAFrameSize);

assignin('base','FrameSize',FrameSize);

end

```

In the project folder, save the file as soc\_hwsw\_init.m in a new subfolder, utilities.

# See Also

"Software and Task Management on Processor" on page 1-61

## **More About**

- "Create a New Project From a Folder" (Simulink)

- "Box and Label Areas of a Model" (Simulink)

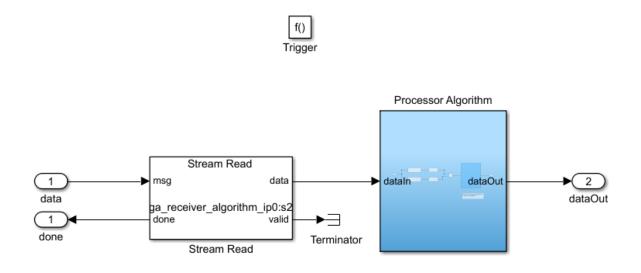

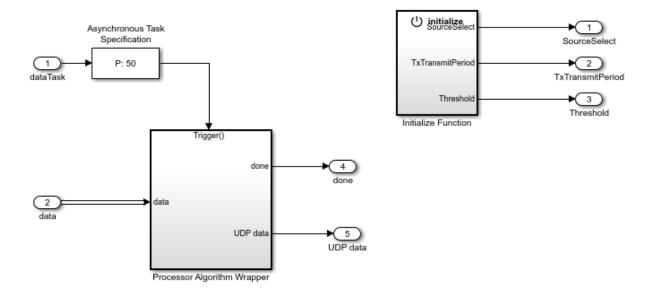

## Software and Task Management on Processor

The processor system in this SoC application reads data from the external memory following a write from the FPGA to that memory. Since FPGA writes and interaction with external memory are asynchronous, the processor uses an event-driven task to read from memory. The software also manages a register on the FPGA that specifies a multiplication factor to be used in the FPGA algorithm.

#### **Processor Model**

- 1 Open a new Simulink model. Save the model as soc\_hwsw\_proc.slx into a new subfolder, named processor, in the project folder.

- 2 Open the configuration parameters of the model. Select the Hardware Implementation tab and set the Hardware board to one of the supported boards for SoC Blockset, such as Xilinx Zynq ZC706 evaluation kit.

**Note** The processor model must use the same hardware board and solver configuration parameter settings as the top level model.

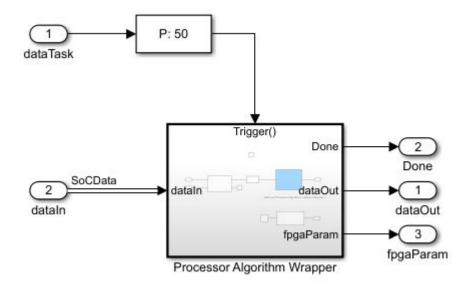

**3** In the model, using a Function-Call Subsystem block, Asynchronous Task Specification block, Inport block, and Outport blocks, create the following system.

- 4 In the dataTask block dialog mask, check **Signal Attributes > Output function** call to expose a function call port on the outside model.

- 5 In the Asynchronous Task Specification block dialog mask, set **Task priority** to 50.

**Note** The task priority of the Asynchronous Task Specification block must match the priority of task in the Task Manager block driving this task.

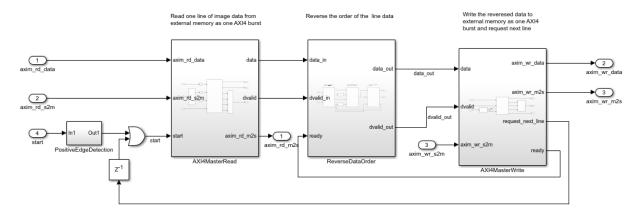

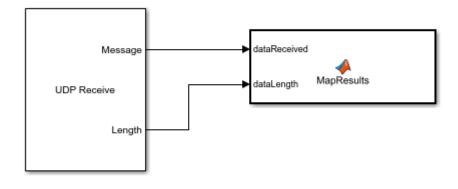

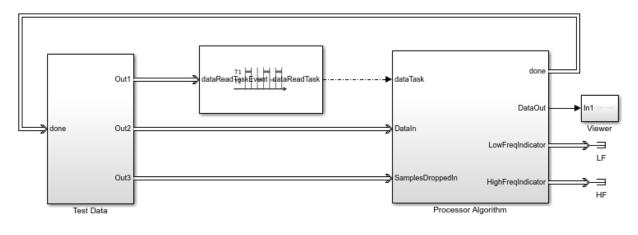

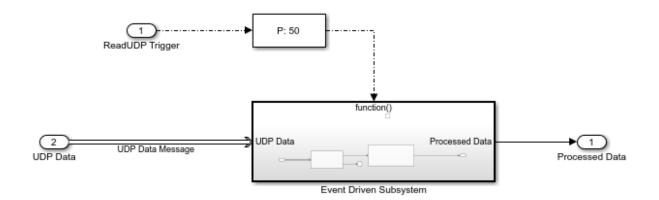

#### **Task Processing**

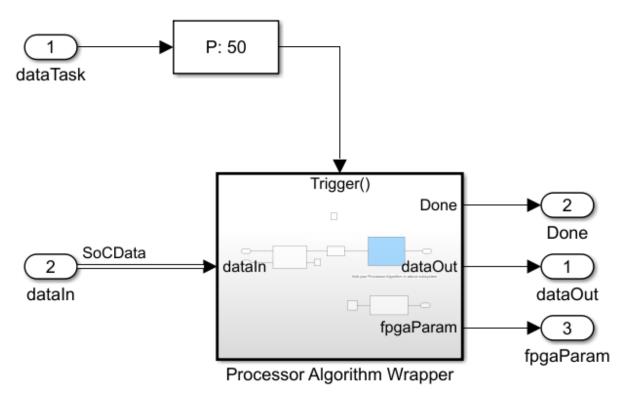

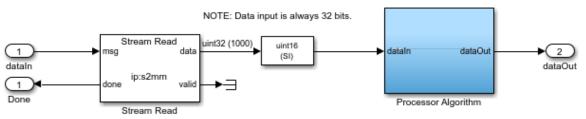

The Processor Algorithm Wrapper subsystem reads data from the external memory only after each write to the external memory by the FPGA.

- 1 Open the Processor Algorithm Wrapper block.

- **2** Using a Stream Read block, Constant block, Data Type Conversion block, and Subsystem blocks, create the following model.

Add your Processor Algorithm in above subsystem

- **3** Open the Stream Read block dialog mask. Set **Number of buffers** to **6**.

- 4 Open the Data Type Conversion block dialog mask and set **Output data type** to uint16.

- 5 The Processor Algorithm subsystem serves as a base to develop your own processing algorithm.

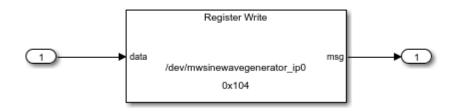

- 6 Open the Register Channel Write subsystem block.

- 7 Add a Register Write block to create the following model.

8 Open the Register Write block dialog mask. Set **Device name** to /dev/ mwsinewavegenerator\_ip0 and **Offset address** to hex2dec('100').

### **Top Model**

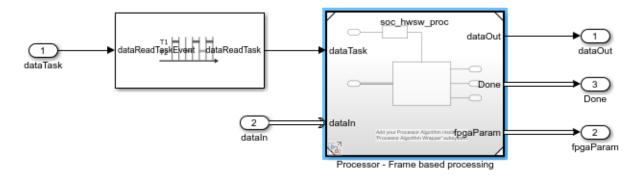

- 1 In the project folder, open the model soc\_hwsw\_top.slx.

- 2 Add a Subsystem block into the Processor area and label the block Processor.

- **3** In the **Processor** subsystem, using the Task Manager block and Model block, create the following system.

- 4 Open the Model block dialog mask and set **Model name** to soc\_hwsw\_proc.slx.

- 5 Open the Task Manager block dialog mask. Set the task Name to dataReadTask and set the Priority to 50. In the Simulation tab, set the Mean, Min, and Max to 8e-05. Click OK.

# See Also

Task Manager

### **More About**

- "What is Task Execution?" on page 1-2

- "Event-Driven Tasks" on page 1-4

- "Task Duration" on page 1-14

## **User Logic on FPGA**

In this SoC project example, the FPGA generates test data and process it in FPGA algorithm before passing it to processor using shared memory.

#### **Sample Based Model**

- 1 Open a new Simulink model. Save the model assoc\_hwsw\_fpga\_sample.slx into the subfolder, named referencedmodels, in the project folder.

- 2 Open the Simulink configuration parameters to the **Hardware Implementation** panel. Set **Hardware board** to None and set **Device vendor** to ASIC/FPGA. In the **Solver** tab, set **Solver selection** > **Type** to Fixed-step. Click **OK** to apply the changes and close the configuration parameters.

**Note** SoC Blockset requires that the FPGA reference models specify the intended deployment hardware, in this case an FPGA.

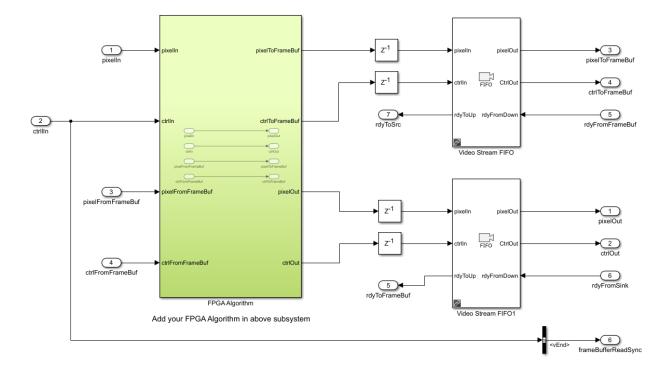

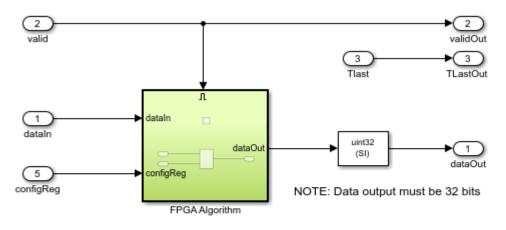

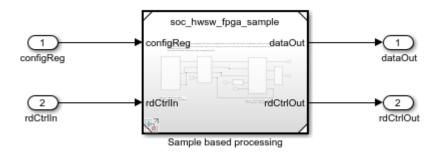

**3** In the new model, using Stream Connector block, SoC Bus Selector block, SoC Bus Creator block, and Subsystem blocks, create the following system.

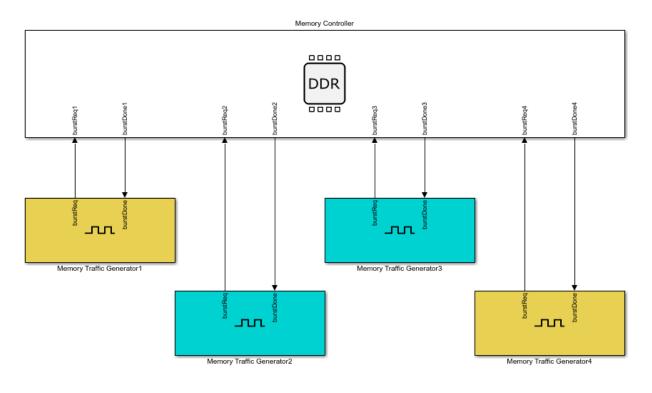

**Tip** When your FPGA model includes more than one IP, you must define each IP as a subsystem and connect the subsystems using a Stream Connector or Video Stream